# 3-Volt System Logic for Personal Computers **Data Book**

© 1993 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This publication neither states nor implies any warranty of any kind, including but not limited to implied warrants of merchantability or fitness for a particular application. AMD® assumes no responsibility for the use of any circuitry other than the circuitry in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

#### **Trademarks**

AMD, Am386, GAL, PAL, PALASM, SKINNYDIP are registered trademarks of Advanced Micro Devices, Inc. GLITCH EATER, LabPro and FlashRITE are trademarks of Advanced Micro Devices, Inc. FusionPLD is a servicemark of Advanced Micro Devices, Inc.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

#### **3-VOLT SYSTEM LOGIC FOR** PERSONAL COMPUTERS DATA BOOK

| Chapter 1   | . Am386® FAMILY PRODUCTS                        |

|-------------|-------------------------------------------------|

| Am386SXLV I | Microprocessor Data Sheet                       |

| Chapter 2   | SMALL COMPUTER SYSTEM INTERFACE (SCSI) PRODUCTS |

| Am53C94LV [ | Data Sheet                                      |

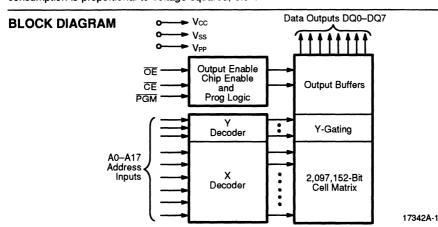

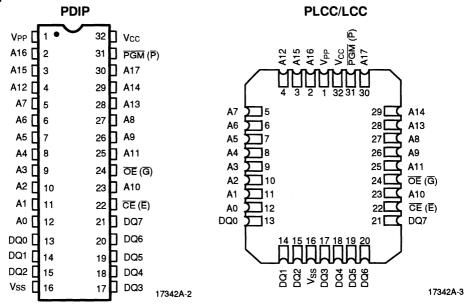

| Chapter 3   | EPROM PRODUCTS                                  |

| Am27LV010/A | \m27LV010B Data Sheet 3-3                       |

| Am27LV020/A | xm27LV020B Data Sheet 3-21                      |

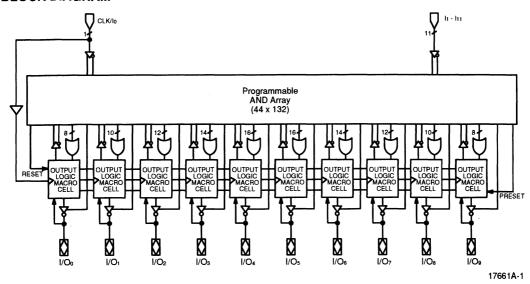

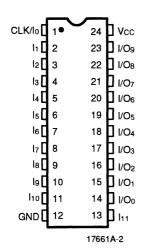

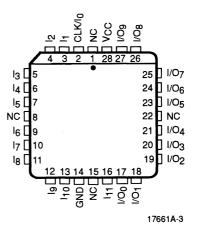

| Chapter 4   | PROGRAMMABLE ARRAY LOGIC (PAL®) PRODUCTS        |

| PALLV16V8Z- | 30 Data Sheet 4-3                               |

| PALLV22V102 | Z-25 Data Sheet                                 |

The desktop revolution has made the personal computer an indispensable business tool. Now, with the recent introduction of 3-volt ICs, designers are breaking the barrier to pervasive portable PC use by extending the useful battery life without weighing down their products. As manufacturers strike the ideal balance between power requirements, useful battery life and weight, users will have virtually unlimited portable machine choices.

AMD's announcement of the world's first 3-volt Am386 microprocessor in October 1991, plus the five other products described in this data book, encouraged designers to optimize designs to produce the battery powered products customers really want. In addition, over 50 other companies have announced various 3-volt components.

AMD recognizes that 3-volt operation alone does not make the ultimate notebook. For this reason, the Am386SXLV and Am386DXLV microprocessors support software power management schemes such as Microsoft's Advanced Power Management (APM) specification and the System Management Mode (SMM) of operation. APM allows the system BIOS, operating system, and APM-compliant applications to share critical power management data while preserving compatibility between hardware and software. SMM allows system hardware or software to interrupt the CPU in order to efficiently control devices and peripherals, further reducing overall power consumption. The combination of APM and SMM plus the overall power savings from 3-volt operation is opening new markets.

The Am386SXLV and Am386DXLV microprocessors provide the enabling technology for a new generation of portable systems, demonstrating AMD's commitment to accelerate the rate of developments for new markets.

In keeping with our philosophy of offering memories that solve customer's needs, AMD is proud to announce a family of 2.7 to 3.6 V EPROMs. This low-voltage family of EPROMs, designated as Am27LV, consists of 1 and 2 Mbit density devices with speeds as fast as 120 ns. In addition, the voltage range for each device has been extended to accommodate systems that have regulated power supplies (3.0 to 3.6 V) and those that are battery operated (2.7 to 3.6 V).

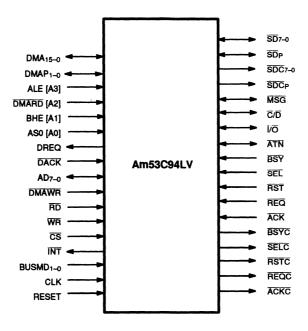

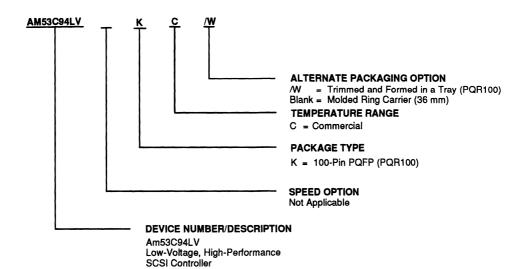

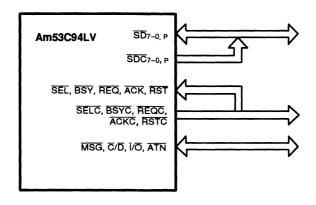

The Am53C94LV is the newest addition to the growing AMD SCSI Family. This device is the first 3.3-V SCSI controller in the market. The Am53C94LV consumes fifty percent less power than 5-V SCSI, while sustaining the same performance as that of the 5-V device (5 Mbyte/s SCSI transfer rate, 20 Mbyte/s DMA transfer rate). It is conveniently packaged in a 100-pin PQFP package to reduce board real estate. The Am53C94LV is the ideal SCSI solution for battery powered peripherals, low power, notebooks, sub-notebooks, and docking stations.

Consistent with AMD's leadership role in the world of programmable logic, AMD is releasing popular PAL®, device architecture for use in 3.3-V systems. The PALLV16V8Z-30 and the PALLV22V10Z-25 will be the first such devices. They are optimized for low-power operation. These low-power devices will provide logic anywhere power comes at a premium. This includes such systems as portable computers, telecommunications, and portable instrumentation.

Successive devices will also be optimized for high performance. These devices will serve those applications that are using 3.3-V advanced technology to push the limits of performance, such as highspeed desktop and mini-computers.

# **Chapter 1**Am386 Family Products

#### CHAPTER 1 Am386 Family Products

| Am386DXLV Microprocessor Data Sheet                                | 1-3  |

|--------------------------------------------------------------------|------|

| Am386SXLV Microprocessor Data Sheet                                | 1-35 |

| Am386DXLV and Am386SXLV Microprocessors Technical Reference Manual | 1-67 |

### Am386DXLV

# Advanced Micro Devices

#### High-Performance, Low-Voltage, 32-Bit Microprocessor

#### **DISTINCTIVE CHARACTERISTICS**

- Operating voltage range 3.0 V to 5.5 V—Ideal for portable PC applications

- ---25-MHz operating frequency for 3.0 V to 5.5 V

- -33-MHz operating frequency for 4.5 V to 5.5 V

- -Twice the battery life of existing 5-V designs

- Wide range of chipsets and other logic available for 3-V systems with support for Standby Mode operation

- -True static design for long battery life

- —Power consumption 85% lower than Intel i386DX, 65% lower than Am386DXL processor

- -Performance on demand (0 to 33 MHz)

- SMM (System Management Mode) for system and power management

- —SMI (System Management Interrupt) for power management independent of processor operating mode and operating system

- —SMI coupled with I/O instruction break feature provides transparent power off and auto resume of peripherals which may not be "power aware"

- —SMI is non-maskable and has higher priority than Non-Maskable Interrupt (NMI)

- Automatic save and restore of the microprocessor state

- Wide range of chipsets supporting SMM available to allow product differentiation

- Lower heat dissipation for fanless systems

- "Float" input to facilitate system debug and test

- Compatible with 386DX systems and software

- Supports 387DX-compatible math coprocessors

- 132-pin PQFP package with optional protective ring for better lead coplanarity

- AMD® advanced 0.8 micron CMOS technology

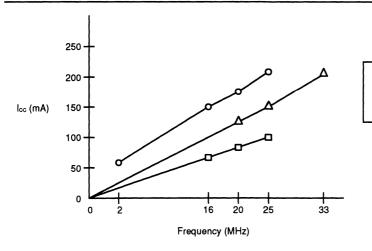

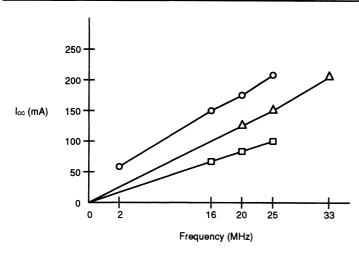

- ntel i386DX @ 5.0 V

- △ Am386DXL CPU @ 5.0 V

- Am386DXLV CPU @ 3.3 V

Note: Inputs at Vcc or Vss.

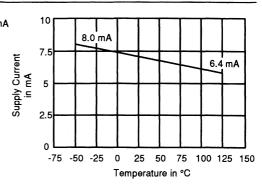

**Typical Power Consumption**

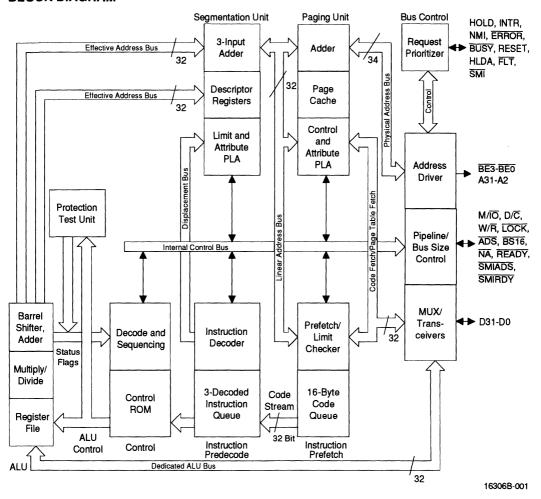

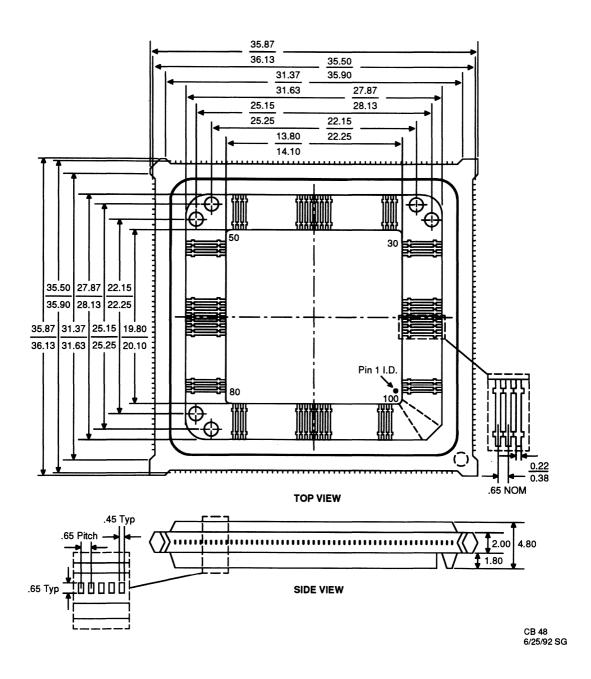

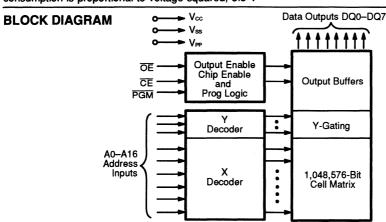

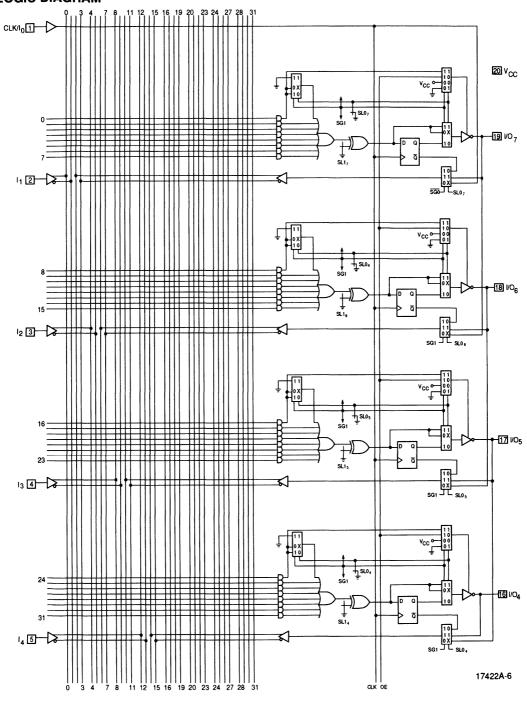

#### **BLOCK DIAGRAM**

#### **GENERAL DESCRIPTION**

The Am386DXLV microprocessor is a low-voltage, true static implementation of the Intel i386DX. The operating voltage range is 3.0 V to 5.5 V. The low-voltage operation makes the Am386DXLV microprocessor ideal for both desktop and battery-powered portable personal computers. For desktop PCs, low heat dissipation allows the system designers to remove or reduce the size and cost of the system cooling fan. The Am386DXLV microprocessor operates at a maximum speed of 25 MHz from 3.0 to 5.5 V and at a maximum speed of 33 MHz from 4.5 to 5.5 V.

The Am386DXLV microprocessor's lower operating voltage and true static design enables longer battery life and/or lower weight for portable applications. At

25 MHz, this device has 80% lower operating lcc than the Intel i386DX. Lowering typical operating voltage from 5.0 V to 3.3 V doubles the battery life. Standby Mode allows the Am386DXLV microprocessor to be clocked down to 0 MHz (DC) and retain full register contents. In Standby Mode, typical current draw is 0.01 mA, a greater than 1000X reduction in power consumption versus the Intel i386DX.

The Am386DXLV processor is available in a small footprint 132-pin Plastic Quad Flat Pack (PQFP) package. This surface-mount package is 40% smaller than a PGA package, allowing smaller lower-cost board designs without the need for a socket. Additionally, the Am386DXLV processors comes with SMM for system and power management. SMI is a non-maskable, higher priority interrupt than NMI and has its own code space (1 Mb in Real Mode and 4 Gb in Protected Mode). SMI can be coupled with the I/O instruction break feature to implement transparent power management of peripherals. SMM can be used by system designers to implement system and power management code independent of the operating system or the processor mode.

The Am386DXLV processor incorporates a float pin that places all outputs in a three-state mode to facilitate board test and debug.

# FUNCTIONAL DESCRIPTION Benefits of Lower Operating Voltage

The Am386DXLV microprocessor has an operating voltage range of 3.0 V to 5.5 V. Low voltage allows for lower operating power consumption, longer battery life, and/or smaller batteries for notebook applications.

Because power is proportional to the square of the voltage, reduction of the supply voltage from 5.0 V to 3.3 V reduces power consumption by 56%. This directly translates to a doubling of battery life for portable applications. Lower power consumption can also be used to reduce the size and weight of the battery. Thus, 3.3-V designs facilitate a reduction in the form factor.

A lower operating voltage results in a reduction of I/O voltage swings. This reduces noise generation and provides a less hostile environment for board design. Lower operating voltage also reduces electromagnetic radiation noise, and makes FCC approval easier to obtain.

#### SMM-System Management Mode

The Am386DXLV processor has a new System Management Mode (SMM) for system and power management. This mode consists of two features: System Management Interrupt (SMI) and I/O instruction break.

#### SMI-System Management Interrupt

SMI is implemented by using special bus interface pins. This interrupt method can be used to perform system management functions such as power management independent of processor operating mode (Real, Protected, or Virtual 8086 Modes).

SMI can also be invoked in software. This allows system software to communicate with SMI power management code. In addition, a UMOV instruction allows data transfers between SMI and normal system memory spaces.

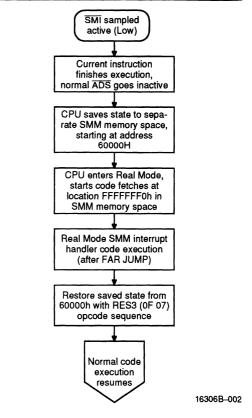

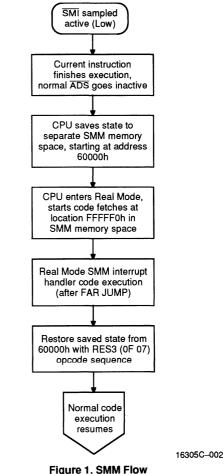

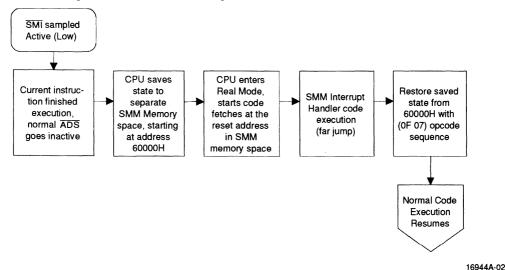

Activating the SMI pin invokes a sequence that saves the operating state of the processor into a separate SMM memory space, independent of the main system memory. After the state is saved, the processor is forced into Real Mode and begins execution at address FFFFFFF0h where a far jump to the SMM code is executed. This Real Mode code can perform its system

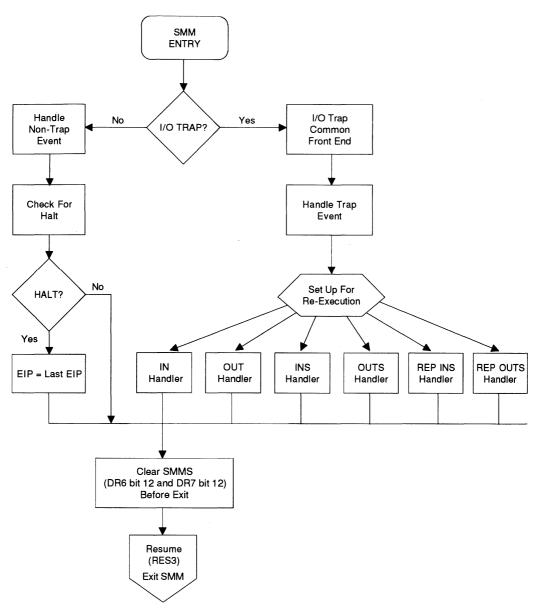

management function and then resume execution of the normal system software by executing an RES3 instruction that will reload the saved processor state and continue execution in the main system memory space. See Figure 1 for a general flowchart of an SMM operation.

Figure 1. SMM Flow

#### CPU Interface—Pin Functions

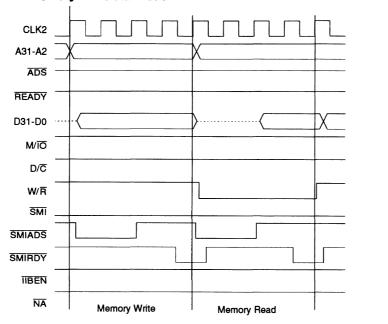

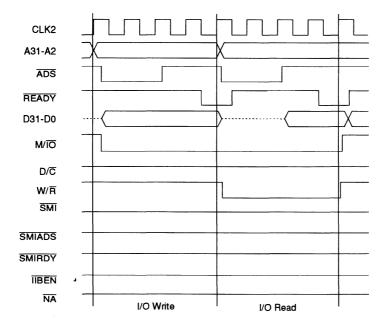

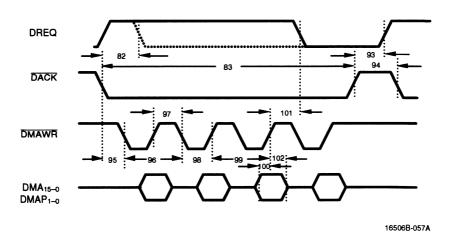

The CPU interface for SMM consists of three pins dedicated to the SMI function. One pin,  $\overline{\text{SMI}}$ , is the new interrupt input. The other two pins,  $\overline{\text{SMIADS}}$  and  $\overline{\text{SMIRDY}}$ , provide the control signals necessary for the separate SMI Mode memory space.

#### **Description of SMM Operation**

The execution of a System Management Interrupt has four distinct phases: the initiation of the interrupt via  $\overline{\text{SMI}}$ , a processor state save, execution of the SMM interrupt code, and a processor state restore (to resume normal operation).

#### Interrupt Initiation

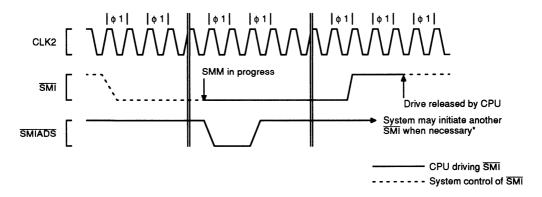

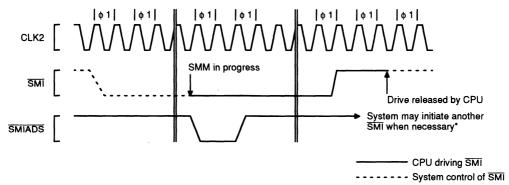

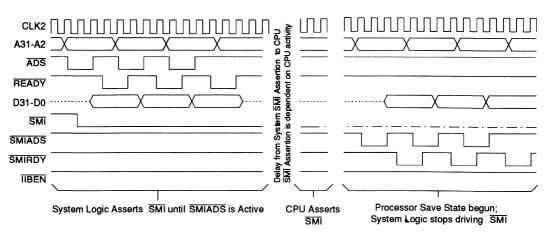

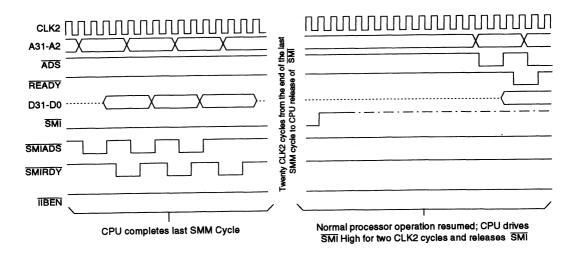

A System Management Interrupt is initiated by the driving of a synchronous, active Low pulse on the SMI pin until the first SMIADS is asserted. This pulse period will ensure recognition of the interrupt. The CPU drives the

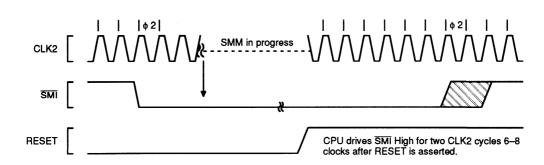

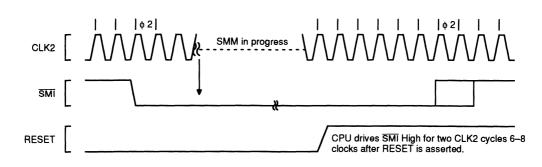

SMI pin active Low after the completion of the current operation (active bus cycle, instruction execution, or both). The active drive of the pin by the CPU is released at the end of the interrupt routine, following the last register read of the saved state. The CPU will drive SMI High for two CLK2 cycles prior to releasing the drive of SMI.

An SMI cannot be masked off by the CPU, and it will always be recognized by the CPU, regardless of operating mode. This includes the Real, Protected, and Virtual 8086 Modes of the processor.

While the CPU is in SMI Mode, a bus hold request via the HOLD pin is granted. The HLDA pin goes active after bus release and the SMIADS pin floats along with the other pins that normally float during a bus hold cycle. The SMI pin does not float during Bus Hold cycles.

#### **Processor State Save**

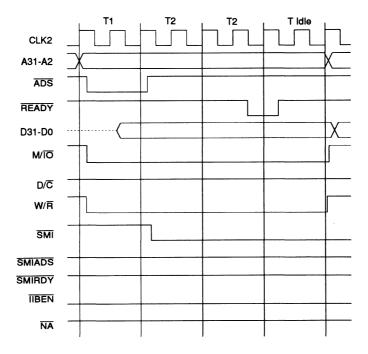

The first set of SMM bus transfer cycles after the CPU's recognition of an active SMI is the processor saving its state to an external RAM array in a separate address space from main system memory. This is accomplished by using the SMIADS and SMIRDY pins for initiation and termination of bus cycles, instead of the ADS and READY pins. The 32-bit addresses to which the CPU saves its state are 60000H–600CBh and 60100h–60127h. These are fixed address locations for each register saved.

Pipelining must be disabled by asserting the  $\overline{\text{NA}}$  pin High in SMM. For  $\overline{\text{ADS}}$  initiated bus cycles,  $\overline{\text{BS16}}$  can be used. The value of  $\overline{\text{BS16}}$  is ignored for  $\overline{\text{SMIADS}}$  initiated bus cycles.

The save state takes approximately 630 CLK2 cycles with zero wait state memory. There are 61 data transfer cycles.

#### **SMI Code Execution**

After the processor state is saved to the separate SMM memory space, the execution of the SMI interrupt routine code begins. The processor enters Real Mode, sets most of the register values to "reset" values (those values normally seen after a CPU reset), and begins fetching code from address FFFFFF0h in the separate SMM memory space. Normally, the first thing the interrupt routine code does is a FAR JUMP to the Real Mode entry point for the SMI interrupt routine, which is also in SMM memory space.

INTR and NMI are disabled upon entry to SMM. See the Am386DXLV/Am386SXLV Microprocessor Technical Manual for further details on interrupts in SMM. The SMM code can be located anywhere within the 1-Mb Real Mode address space, except where the processor state is saved. I/O cycles, as a result of the IN, OUT, INS, and OUTS instructions, will go to the normal address space, utilizing the normal ADS and READY bus interface signals. This facilitates power management code manipulating system hardware registers as

needed through the standard I/O subsystem; a separate I/O space is not implemented.

# Processor State Restore (Resuming Normal Execution)

Returning to normal code execution in the main system memory, including restoring the processor operating mode, is accomplished by executing a RES3 (0Fh 07h) instruction. This instruction invokes a restore CPU state operation that reloads the CPU registers from the saved data in the RAM controlled by SMIADS and SMIRDY.

The ES:EDI register pair must point to the physical address of the saved state, this is normally at 60000h. In Real Mode, the address is calculated as ES·16+EDI. The saved state should not cross a 64K boundary. The special opcode sequence RES3 should be executed to start the restore state operation. After completion of the restore state operation, the SMI pin will be deactivated by the CPU and normal code execution will continue at the point where it left off before the SMI occurred.

In a zero wait state memory implementation, approximately 574 CLK2 cycles complete the restore state operation. There are 61 data transfer cycles.

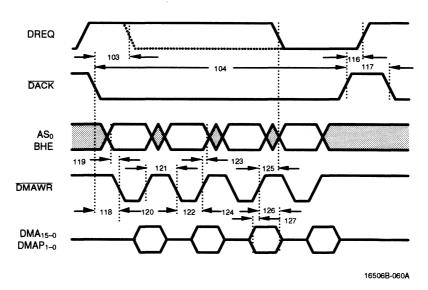

#### Software Features

There are several features of the SMI function that provide support for special operations during the execution of the system's software. These features involve the execution of reserved opcodes to induce specific SMI related operations.

#### Software SMI Generation

Besides hardware initiation of the System Management Interrupt via the SMI pin, there is also a software induced SMI mechanism. Generating a soft SMI involves setting a control bit 12 in Debug Register 7 (DR7) and executing an SMI instruction (reserved opcode F1h).

The functional sequence of the software-based SMI is identical to the hardware-based SMI with the exception that the SMI pin is not initially driven active by an external source. Upon execution of a soft SMI opcode, the SMI pin is driven active (Low) by the processor before the save state operation begins.

#### **Memory Transfers to Main System Memory**

While executing an SMI routine, the interrupt code can initiate memory data reads and writes to the main system memory using the normal ADS and READY pins. This is accomplished by using reserved opcodes that are special forms of the MOV instruction (called UMOV). The UMOV opcodes can move byte, word, or doubleword register operands to or from main system memory. Multiple data transfers using the normal ADS and READY pins will occur if the operands are misaligned relative to the effective address used. The UMOV opcodes are 0Fh 10h, 0Fh 11h, 0Fh 12h, and 0Fh 13h.

The UMOV instruction can use any of the 386 addressing modes, as specified in the ModR/M byte of the opcode. Note that the 16- and 32-bit versions are the same opcodes with the exception of the 66h operand size prefix. The BS16 line is recognized during the normal memory space data transfer(s) initiated by these instructions.

#### I/O Instruction Break

The Am386DXLV processor has an I/O instruction break feature that allows the system logic to implement I/O trapping for peripheral devices. To enable the I/O instruction break feature, IIBEN must first be asserted active Low. On detecting an I/O instruction, the processor prevents the execution unit from executing further instructions until READY is driven active Low by the system. Once READY is driven active, the execution unit either immediately responds to any active interrupt request or continues executing instructions following the I/O instruction that caused the break.

The I/O instruction break feature can be used to allow system logic to implement I/O trapping for peripheral devices. On sensing an I/O instruction, the system drives the  $\overline{SMI}$  interrupt active before driving  $\overline{READY}$  active. This ensures that the service routine is executed immediately following the I/O instruction that caused the break. (If the I/O instruction break feature is not enabled via  $\overline{IIBEN}$ , several instructions that follow the I/O instruction that caused the break will execute before the SMI service routine is executed.) The SMI service routine can access the peripheral for which  $\overline{SMI}$  was asserted and modify the peripheral's state.

The SMI service routine normally returns to the instruction following the I/O instruction that caused the break. By modifying the saved state instruction pointer, the routine can choose to return to the I/O instruction that caused the break and re-execute that instruction. The default is to return to the following instruction (except for REP I/O strings). To re-execute the I/O instruction that caused the break, the SMI service routine must copy the I/O instruction pointer over the default pointer. This feature is particularly useful when an application program requests an access to a peripheral that has been powered down. The SMI service routine can restore power to the peripheral and initiate a re-execution sequence transparent to the application program. This reexecution feature should only be used if the SMI is in response to an I/O trap with IIBEN active.

Note that the I/O instruction break feature is not enabled for memory mapped I/O devices or for 80387 bus cycles, even if IIBEN is active.

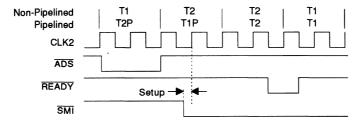

#### I/O Instruction Break Timing

The I/O Instruction Break feature requires that  $\overline{\text{SMI}}$  be sampled active (Low) by the processor at least three CLK2 edges before the CLK2 edge that ends the I/O

cycle with an active READY signal. This timing applies for both pipelined and non-pipelined cycles. If this timing constraint is not met, additional instructions may be executed by the internal execution unit prior to entering SMI Mode.

Depending on the state of the prefetch queue at the time SMI is asserted, instruction fetch cycles may occur on the normal ADS interface before the SMI save state process begins with the assertion of SMIADS. However, this fetched code will not be executed.

#### **True Static Operation**

The Am386DXLV microprocessor incorporates a true static design. Unlike dynamic circuit design, the Am386DXLV device eliminates the minimum operating frequency restriction. It may be clocked from its maximum speed all the way down to 0 MHz (DC). System designers can use this feature to design true 32-bit battery-powered portable PCs with long battery life.

#### Standby Mode

This true static design of the Am386DXLV microprocessor allows for a Standby Mode. At any of its operating speeds, the Am386DXLV microprocessor will retain its state (i.e., the contents of all of its registers). By shutting off the clock completely, the device enters Standby Mode. Since power consumption is a function of clock frequency, operating power consumption is reduced as the frequency is lowered. In Standby Mode, typical current draw is reduced to less than 0.01 mA at DC. This feature not only saves battery life, but it also simplifies the design of power-conscious notebook computers in the following ways.

- Eliminates the need for software in BIOS to save and restore the contents of registers.

- Allows simpler circuitry to control stopping of the clock since the system does not need to know the state of the processor.

#### **Lower Operating Icc**

True static design also allows lower operating lcc when operating at any speed.

#### Performance on Demand

The Am386DXLV microprocessor retains its state at any speed from 0 MHz (DC) to its maximum operating speed. With this feature, system designers may vary the operating speed of the system to extend the battery life in portable systems.

For example, the system could operate at low speeds during inactivity or polling operations. However, upon interrupt, the system clock can be increased up to its maximum speed. After a user-defined time-out period, the system can be returned to a low (or 0 MHz) operating speed without losing its state. This design maximizes battery life while achieving optimal performance.

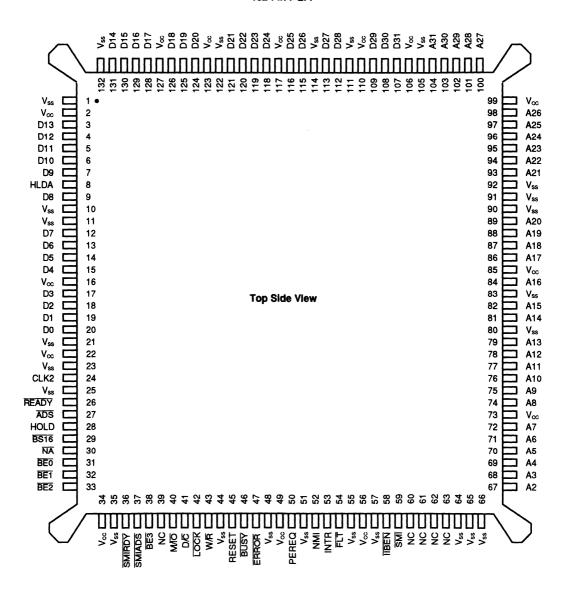

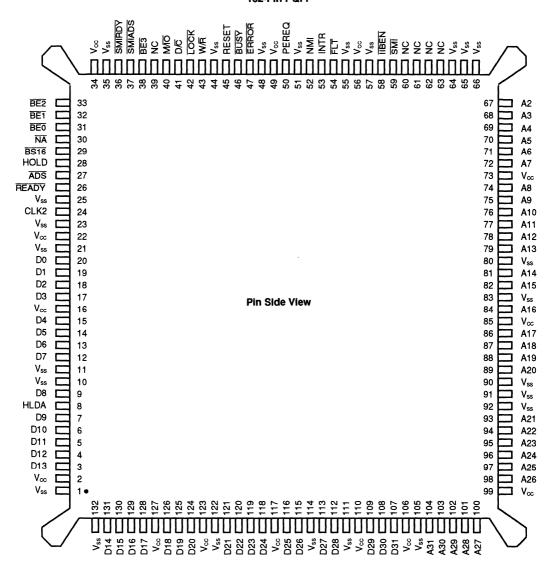

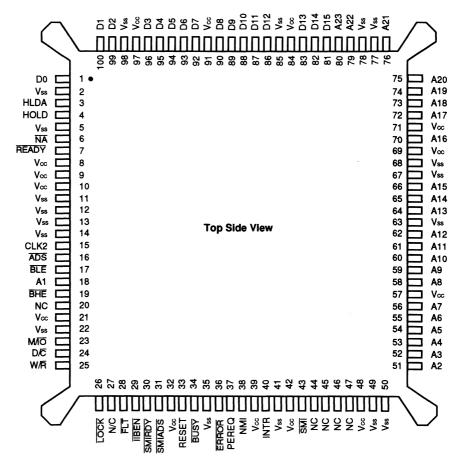

#### **CONNECTION DIAGRAM**

#### 132-Lead Plastic Quad Flat Pack (PQFP) Package — Top Side View

#### 132-Pin PQFP

Notes: Pin 1 is marked for orientation.

NC = Not connected; connection of an NC pin may cause a malfunction or incompatibility with future shippings of the Am386DXLV microprocessor.

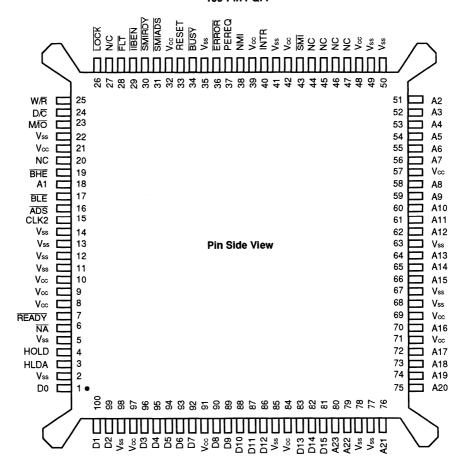

#### **CONNECTION DIAGRAM**

#### 132-Lead Plastic Quad Flat Pack (PQFP) Package — Pin Side View

#### 132-Pin PQFP

Notes: Pin 1 is marked for orientation.

NC = Not connected; connection of an NC pin may cause a malfunction or incompatibility with future shippings of the Am386DXLV microprocessor.

### **PQFP Pin Designations (Sorted by Functional Grouping)**

| Pin<br>Name | Pin<br>No. |

|-------------|------------|-------------|------------|-------------|------------|-------------|------------|-------------|------------|-------------|------------|

| A2          | 67         | A24         | 96         | D6          | 13         | D28         | 112        | Vcc         | 16         | Vss         | 51         |

| A3          | 68         | A25         | 97         | D7          | 12         | D29         | 109        |             | 22         |             | 55         |

| A4          | 69         | A26         | 98         | D8          | 9          | D30         | 108        |             | 34         |             | 57         |

| A5          | 70         | A27         | 100        | D9          | 7          | D31         | 107        |             | 49         |             | 64         |

| A6          | 71         | A28         | 101        | D10         | 6          | D/C         | 41         |             | 56         |             | 65         |

| A7          | 72         | A29         | 102        | D11         | 5          | ERROR       | 47         |             | 73         |             | 66         |

| A8          | 74         | A30         | 103        | D12         | 4          | FLT         | 54         |             | 85         |             | 80         |

| A9          | 75         | A31         | 104        | D13         | 3          | HLDA        | 8          |             | 99         |             | 83         |

| A10         | 76         | ADS         | 27         | D14         | 131        | HOLD        | 28         |             | 106        |             | 90         |

| A11         | 77         | BEO         | 31         | D15         | 130        | IIBEN       | 58         |             | 110        |             | 91         |

| A12         | 78         | BE1         | 32         | D16         | 129        | INTR        | 53         |             | 117        |             | 92         |

| A13         | 79         | BE2         | 33         | D17         | 128        | LOCK        | 42         |             | 123        | ĺ           | 105        |

| A14         | 81         | BE3         | 38         | D18         | 126        | M/IO        | 40         |             | 127        |             | 111        |

| A15         | 82         | BS16        | 29         | D19         | 125        | NA          | 30         | Vss         | 1          | l           | 114        |

| A16         | 84         | BUSY        | 46         | D20         | 124        | NMI         | 52         |             | 10         |             | 122        |

| A17         | 86         | CLK2        | 24         | D21         | 121        | PEREQ       | 50         |             | 11         |             | 132        |

| A18         | 87         | D0          | 20         | D22         | 120        | READY       | 26         |             | 21         | W/R         | 43         |

| A19         | 88         | D1          | 19         | D23         | 119        | RESET       | 45         |             | 23         | NC          | 39         |

| A20         | 89         | D2          | 18         | D24         | 118        | SMI         | 59         |             | 25         |             | 60         |

| A21         | 93         | D3          | 17         | D25         | 116        | SMIADS      | 37         |             | 35         | l           | 61         |

| A22         | 94         | D4          | 15         | D26         | 115        | SMIRDY      | 36         |             | 44         |             | 62         |

| A23         | 95         | D5          | 14         | D27         | 113        | Vcc         | 2          |             | 48         |             | 63         |

### PQFP Pin Designations (Sorted by Pin Number)

| Pin<br>No. | Pin<br>Name |

|------------|-------------|------------|-------------|------------|-------------|------------|-------------|------------|-------------|------------|-------------|

| 1          | Vss         | 23         | Vss         | 45         | RESET       | 67         | <b>A</b> 2  | 89         | A20         | 111        | Vss         |

| 2          | Vcc         | 24         | CLK2        | 46         | BUSY        | 68         | A3          | 90         | Vss         | 112        | D28         |

| 3          | D13         | 25         | Vss         | 47         | ERROR       | 69         | A4          | 91         | Vss         | 113        | D27         |

| 4          | D12         | 26         | READY       | 48         | Vss         | 70         | <b>A</b> 5  | 92         | Vss         | 114        | VSS         |

| 5          | D11         | 27         | ADS         | 49         | Vcc         | 71         | A6          | 93         | A21         | 115        | D26         |

| 6          | D10         | 28         | HOLD        | 50         | PEREQ       | 72         | <b>A</b> 7  | 94         | A22         | 116        | D25         |

| 7          | D9          | 29         | BS16        | 51         | Vss         | 73         | Vcc         | 95         | A23         | 117        | Vcc         |

| 8          | HLDA        | 30         | NA          | 52         | NMI         | 74         | <b>A8</b>   | 96         | A24         | 118        | D24         |

| 9          | D8          | 31         | BE0         | 53         | INTR        | 75         | <b>A9</b>   | 97         | A25         | 119        | D23         |

| 10         | Vss         | 32         | BE1         | 54         | FLT         | 76         | A10         | 98         | A26         | 120        | D22         |

| 11         | Vss         | 33         | BE2         | 55         | Vss         | 77         | A11         | 99         | Vcc         | 121        | D21         |

| 12         | D7          | 34         | Vcc         | 56         | Vcc         | 78         | A12         | 100        | A27         | 122        | Vss         |

| 13         | D6          | 35         | Vss         | 57         | Vss         | 79         | A13         | 101        | A28         | 123        | Vcc         |

| 14         | D5          | 36         | SMIRDY      | 58         | IIBEN       | 80         | Vss         | 102        | A29         | 124        | D20         |

| 15         | D4          | 37         | SMIADS      | 59         | SMI         | 81         | A14         | 103        | A30         | 125        | D19         |

| 16         | Vcc         | 38         | BE3         | 60         | NC          | 82         | A15         | 104        | A31         | 126        | D18         |

| 17         | D3          | 39         | NC          | 61         | NC          | 83         | $V_{ss}$    | 105        | Vss         | 127        | Vcc         |

| 18         | D2          | 40         | M/IO        | 62         | NC          | 84         | A16         | 106        | Vcc         | 128        | D17         |

| 19         | D1          | 41         | D/C         | 63         | NC          | 85         | Vcc         | 107        | D31         | 129        | D16         |

| 20         | D0          | 42         | LOCK        | 64         | Vss         | 86         | A17         | 108        | D30         | 130        | D15         |

| 21         | Vss         | 43         | W/R         | 65         | Vss         | 87         | A18         | 109        | D29         | 131        | D14         |

| 22         | Vcc         | 44         | Vss         | 66         | Vss         | 88         | A19         | 110        | Vcc         | 132        | Vss         |

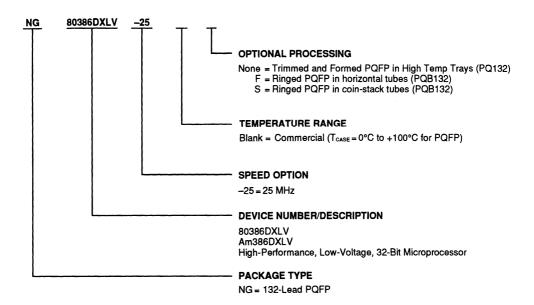

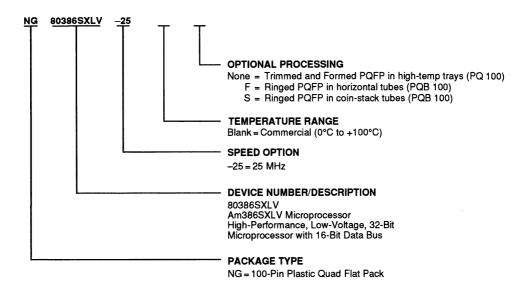

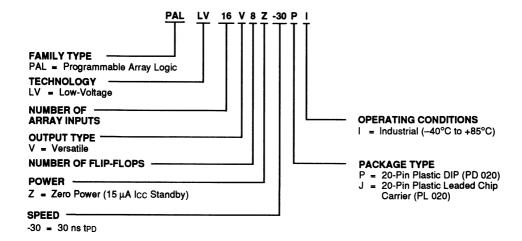

#### **ORDERING INFORMATION**

#### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the elements below.

| Valid Combinations |           |                     |  |  |  |

|--------------------|-----------|---------------------|--|--|--|

| NG                 | 80386DXLV | -25<br>-25F<br>-25S |  |  |  |

#### **Valid Combinations**

Valid Combinations lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

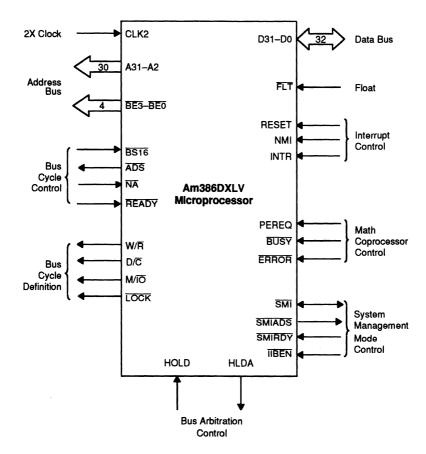

### LOGIC SYMBOL

#### AMD

#### PIN DESCRIPTION

#### A31-A2

#### Address Bus (Outputs)

Outputs physical memory or port I/O addresses.

#### ADS

#### Address Status (Active Low; Output)

Indicates that a valid bus cycle definition and address (W/R, D/O, M/IO, BE3-BE0, and A31-A2) are being driven at the Am386DXLV microprocessor pins. Bus cycles initiated by ADS must be terminated by READY.

#### BE3-BE0

#### Byte Enable (Active Low; Outputs)

Indicates which data bytes of the data bus take part in a bus cycle.

#### **BS16**

#### Bus Size 16 (Active Low; Input)

Allows direct connection of 32-bit and 16-bit data buses. BS16 has an internal pull-up resistor.

#### BUSY

#### **Busy (Active Low; Input)**

Signals a busy condition from a processor extension. BUSY has an internal pull-up resistor.

#### CLK<sub>2</sub>

#### Clock (Input)

Provides the fundamental timing for the Am386DXLV microprocessor.

#### D31-D0

#### Data Bus (Inputs/Outputs)

Inputs data during memory, I/O, and interrupt acknowledge read cycles and outputs data during memory and I/O write cycles.

#### D/C

#### Data/Control (Output)

A bus cycle definition pin that distinguishes data cycles, either memory or I/O, from control cycles (which are interrupt acknowledge, halt, and instruction fetching).

#### ERROR

#### Error (Active Low; Input)

Signals an error condition from a processor extension. ERROR has an internal pull-up resistor.

#### FLT

#### Float (Active Low; Input)

An input signal which forces all bidirectional and output signals, including HLDA, to the three-state condition. FLT has an internal pull-up resistor.

#### **HLDA**

#### **Bus Hold Acknowledge (Active High; Output)**

Indicates that the Am386DXLV microprocessor has surrendered control of its local bus to another bus master.

#### HOLD

#### **Bus Hold Request (Active High; Input)**

Allows another bus master to request control of the local bus.

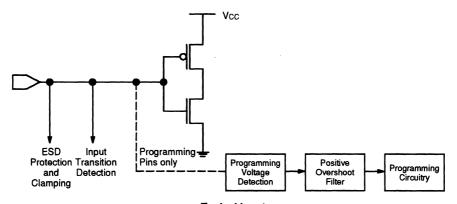

#### **IIBEN**

#### I/O Instruction Break Enable (Active Low; Input)

Enables the I/O instruction break feature. IIBEN has an internal pull-up resistor. Once IIBEN is driven active Low, the internal pull-up resistor is disabled until the CPU is reset.

#### INTR

#### Interrupt Request (Active High; Input)

A maskable input that signals the Am386DXLV microprocessor to suspend execution of the current program and execute an interrupt acknowledge function.

#### LOCK

#### **Bus Lock (Active Low; Output)**

A bus cycle definition pin that indicates that other system bus masters are denied access to the system bus while it is active.

#### M/IO

#### Memory I/O (Output)

A bus cycle definition pin that distinguishes memory cycles from input/output cycles.

#### NA

#### **Next Address (Active Low; Input)**

Used to request address pipelining.

#### NC

#### **No Connect**

Should always remain unconnected. Connection of an NC pin may cause the processor to malfunction or be incompatible with future steppings of the Am386DXLV microprocessor.

#### IMN

## Non-Maskable Interrupt Request (Active High; Input)

A non-maskable input that signals the Am386DXLV microprocessor to suspend execution of the current program and execute an interrupt acknowledge function.

#### **PEREQ**

#### **Processor Extension Request (Active High; Input)**

Indicates that the processor extension has data to be transferred by the Am386DXLV microprocessor. PEREQ has an internal pull-down resistor.

#### READY

#### **Bus Ready (Active Low; Input)**

Terminates the bus cycle initiated by ADS.

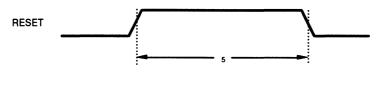

#### RESET

#### Reset (Active High; Input)

Suspends any operation in progress and places the Am386DXLV microprocessor in a known reset state.

#### SMI

# System Management Interrupt (Active Low; Input/Output)

A Non-Maskable Interrupt (NMI) pin that signals the Am386DXLV microprocessor to suspend execution and enter System Management Mode. SMI has a dynamic pull-up resistor that is disabled when the processor is in SMM. SMI is not three-stated during hold acknowledge bus cycles.

#### **SMIADS**

# SMI Address Status (Active Low, Three-State; Output)

Indicates that a valid bus cycle definition and address (W/R, D/O, M/IO, BE3-BE0, and A31-A2) are being driven at the Am386DXLV microprocessor pins while in System Management Mode. Bus cycles initiated by SMIADS must be terminated by SMIRDY.

#### **SMIRDY**

#### SMI Ready (Active Low; input)

This input terminates the current bus cycle to the SMM address space in the same manner the READY pin does for the Normal Mode address space. SMIRDY has an internal pull-up resistor. SMIRDY must not be tied to READY.

#### Vcc

#### System Power (Active High; Input)

Provides the DC supply input.

#### Vss

#### **System Ground (Input)**

Provides 0-V connection from which all inputs and outputs are measured.

#### W/R

#### Write/Read (Output)

A bus cycle definition pin that distinguishes write cycles from read cycles.

#### **ABSOLUTE MAXIMUM RATINGS**

Storage Temperature ..... -65°C to +150°C Ambient Temperature Under Bias .. -65°C to +125°C

Stresses above those listed may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to ABSOLUTE MAXIMUM RATINGS for extended periods may affect device reliability.

#### **OPERATING RANGES**

Supply Voltage with Respect to  $V_{SS}$  . . -0.5 V to +7 V Voltage on Other Pins . . . . . -0.5 V to  $V_{CC}$  +0.5 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

#### DC CHARACTERISTICS over COMMERCIAL Operating Ranges

$V_{CC} = 3.0 \text{ V to } 3.6 \text{ V}; T_{CASE} = 0^{\circ}\text{C to } +100^{\circ}\text{C}$

|                  |                                                                                                                                                                                |                                                                               | F                      | Final                   |             |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------|-------------------------|-------------|--|

| Symbol           | Parameter Description                                                                                                                                                          | Notes                                                                         | Min                    | Max                     | Unit        |  |

| VıL              | Input Low Voltage                                                                                                                                                              | (Note 1)                                                                      | -0.3                   | 0.8                     | ٧           |  |

| V <sub>IH</sub>  | Input High Voltage                                                                                                                                                             |                                                                               | 2.0                    | V <sub>cc</sub> + 0.3   | V           |  |

| V <sub>ILC</sub> | CLK2 Input Low Voltage                                                                                                                                                         | (Note 1)                                                                      | -0.3                   | 0.8                     | V           |  |

| V <sub>IHC</sub> | CLK2 Input High Voltage (25 MHz)                                                                                                                                               |                                                                               | 2.4                    | V <sub>cc</sub> + 0.3   | ٧           |  |

| Vol              | Output Low Voltage<br>I <sub>OL</sub> = 0.5 mA: A31-A2, D31-D0                                                                                                                 | (Note 5)                                                                      |                        | 0.2                     | ٧           |  |

|                  | lot = 0.5 mA: BE3-BE0, W/R, D/C, M/IO,<br>LOCK, ADS, SMIADS, HLDA, SMI<br>lot = 2 mA: A31-A2, D31-D0<br>lot = 2.5 mA: BE3-BE0, W/R, D/C, M/IO,<br>LOCK, ADS, SMIADS, HLDA, SMI |                                                                               |                        | 0.2<br>0.45<br>0.45     | V<br>V<br>V |  |

| V <sub>он</sub>  | Output High Voltage                                                                                                                                                            | (Note 5)                                                                      |                        |                         |             |  |

|                  | I <sub>он</sub> = 0.1 mA: A31-A2, D31-D0                                                                                                                                       | (Note 6)                                                                      | V <sub>cc</sub> −0.2   |                         | ٧           |  |

|                  | I <sub>OH</sub> = 0.1 mA: BE3-BE0,<br>W/R, D/C, M/IO, LOCK,<br>ADS, SMIADS, HLDA, SMI                                                                                          |                                                                               | V <sub>cc</sub> -0.2   |                         | ٧           |  |

|                  | I <sub>он</sub> = 0.5 mA: A31-A2, D31-D0                                                                                                                                       |                                                                               | V <sub>cc</sub> −0.45  |                         | V           |  |

|                  | I <sub>OH</sub> = 0.5 mA: BE3-BE0,<br>W/R, D/C, M/IO, LOCK,<br>ADS, SMIADS, HLDA, SMI                                                                                          |                                                                               | V <sub>cc</sub> – 0.45 |                         | ٧           |  |

| lu               | Input Leakage Current (All pins except BS16, PEREQ, IIBEN, BUSY, FLT, ERROR, SMI, and SMIRDY)                                                                                  | 0 V ≤ V <sub>IN</sub> ≤ V <sub>⊙</sub><br>(Note 7)                            |                        | ±10                     | μА          |  |

| lin              | Input Leakage Current<br>(PEREQ Pin)                                                                                                                                           | V <sub>IH</sub> = V <sub>CC</sub> - 0.1 V<br>V <sub>IH</sub> = 2.4 V (Note 2) |                        | 300<br>200              | μΑ          |  |

| l <sub>IL</sub>  | Input Leakage Current<br>(BS16, BUSY, FLT, ERROR, SMI, IIBEN,<br>and SMIRDY)                                                                                                   | V <sub>IL</sub> = 0.1 V<br>V <sub>IL</sub> = 0.45 V (Note 3)                  |                        | -300<br>-200            | μА          |  |

| اده              | Output Leakage Current                                                                                                                                                         | 0.1 V ≤ V <sub>out</sub> ≤ V <sub>cc</sub>                                    |                        | ±15                     | μΑ          |  |

| lcc              | Supply Current (Note 8)                                                                                                                                                        | V <sub>cc</sub> = 3.3 V                                                       |                        | V <sub>cc</sub> = 3.6 V |             |  |

|                  | CLK2=40 MHz: Oper. Freq. 20 MHz                                                                                                                                                | Icc Typ = 80                                                                  |                        | 95                      | mA          |  |

|                  | CLK2 = 50 MHz: Oper. Freq. 25 MHz                                                                                                                                              | lcc Typ = 95                                                                  |                        | 115                     | mA          |  |

| Iccsa            | Standby Current (Note 8)                                                                                                                                                       | I <sub>ccsB</sub> Typ = 10 μA                                                 |                        | 150                     | μA          |  |

| Cin              | Input or I/O Capacitance                                                                                                                                                       | Fc=1 MHz (Note 4)                                                             | <b>_</b>               | 10                      | pF          |  |

| Соит             | Output Capacitance                                                                                                                                                             | Fc=1 MHz (Note 4)                                                             | <b>_</b>               | 12                      | pF          |  |

| Cclk             | CLK2 Capacitance                                                                                                                                                               | F <sub>c</sub> = 1 MHz (Note 4)                                               |                        | 20                      | pF          |  |

- Notes: 1. The Min value, -0.3, is not 100% tested.

- 2. PEREQ input has an internal pull-down resistor.

- 3. BS16, BUSY, FLT, ERROR, SMI, SMIRDY, and IIBEN inputs each have an internal pull-up resistor.

- 4. Not 100% tested.

- 5. Outputs are CMOS and will pull rail-to-rail if the load is not resistive.

- 6.  $V_{\text{OH}}$  is only valid for  $\overline{\text{SMI}}$  when exiting SMM for two CLK2 cycles.

- 7. SMI and IIBEN leakage Low will be ILI when pull-up is inactive and IIL when pull-up is active.

- 8. Inputs are at either Vcc or Vss.

#### **ABSOLUTE MAXIMUM RATINGS**

Storage Temperature  $\dots -65^{\circ}\text{C}$  to +150°C Ambient Temperature Under Bias  $\dots -65^{\circ}\text{C}$  to +125°C

Stresses above those listed may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to ABSOLUTE MAXIMUM RATINGS for extended periods may affect device reliability.

#### **OPERATING RANGES**

Supply Voltage with Respect

to Vss ..... -0.5 V to +7 V

Voltage on Other Pins . . . . . . . -0.5 V to  $V_{\rm CC}$  +0.5 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

#### **DC CHARACTERISTICS** over **COMMERCIAL** Operating Ranges

$V_{CC} = 3.6 \text{ V to } 5.5 \text{ V}; T_{CASE} = 0^{\circ}\text{C to } +100^{\circ}\text{C}$

|                 |                                                                                                        |                                                     |      | Final                   | <u> </u> |

|-----------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------|-------------------------|----------|

| Symbol          | Parameter Description                                                                                  | Notes                                               | Min  | Max                     | Unit     |

| VIL             | Input Low Voltage                                                                                      | (Note 1)                                            | -0.3 | 0.8                     | V        |

| ViH             | Input High Voltage                                                                                     |                                                     | 2.0  | V <sub>cc</sub> + 0.3   | V        |

| Vilc            | CLK2 Input Low Voltage                                                                                 | (Note 1)                                            | -0.3 | 0.8                     | V        |

| Vihc            | CLK2 Input High Voltage (33 MHz)                                                                       |                                                     | 2.7  | V <sub>cc</sub> + 0.3   | V        |

| VoL             | Output Low Voltage IoL = 4 mA: A31-A2, D31-D0                                                          | (Note 5)                                            |      | 0.45                    | ٧        |

|                 | lo∟=5 mA: BE3–BE0, W/R, D/Ō,<br>M/iŌ, LŌCK, ADS, SMIADS,<br>HLDA, SMI                                  |                                                     |      | 0.45                    | ٧        |

| V <sub>он</sub> | Output High Voltage                                                                                    | (Note 5)                                            |      |                         |          |

|                 | I <sub>он</sub> = 1 mA: A31-A2, D31-D0                                                                 | (Note 6)                                            | 2.4  |                         | V        |

|                 | I <sub>oh</sub> = 0.9 mA: BE3-BE0,W/R,<br>D/C, M/IO, LOCK, ADS,<br>SMIADS, HLDA, SMI                   |                                                     | 2.4  |                         | ٧        |

| lu              | Input Leakage Current<br>(All pins except BS16, PEREQ,<br>IIBEN, BUSY, FLT, SMI, SMIRDY,<br>and ERROR) | 0 V ≤ V <sub>IN</sub> ≤ V <sub>CC</sub><br>(Note 7) |      | ±15                     | μА       |

| l <sub>IH</sub> | Input Leakage Current<br>(PEREQ Pin)                                                                   | V <sub>H</sub> = 2.4 V<br>(Note 2)                  |      | 200                     | μА       |

| lı.             | Input Leakage Current<br>(BS16, BUSY, FLT, SMI, SMIRDY,<br>IIBEN, and ERROR)                           | V <sub>IL</sub> = 0.45<br>(Note 3)                  |      | -400                    | μА       |

| lιο             | Output Leakage Current                                                                                 | 0.45 V ≤ V <sub>out</sub> ≤ V <sub>cc</sub>         |      | ±15                     | μА       |

| lcc             | Supply Current (Note 8)                                                                                | Vcc = 5.0 V                                         |      | V <sub>cc</sub> = 5.5 V | 1        |

|                 | CLK2 = 40 MHz: Oper. Freq. 20 MHz                                                                      | lcc Typ = 130                                       |      | 155                     | mA       |

|                 | CLK2 = 50 MHz: Oper. Freq. 25 MHz                                                                      | lcc Typ = 160                                       |      | 190                     | mA       |

|                 | CLK2 = 66 MHz: Oper. Freq. 33 MHz                                                                      | lcc Typ = 210                                       |      | 245                     | mA       |

| Iccsa           | Standby Current (Note 8)                                                                               | Iccsa Typ = 20 μA                                   |      | 150                     | μА       |

| Cin             | Input or I/O Capacitance                                                                               | Fc=1 MHz (Note 4)                                   |      | 10                      | pF       |

| Соит            | Output Capacitance                                                                                     | Fc=1 MHz (Note 4)                                   |      | 12                      | pF       |

| Cclk            | CLK2 Capacitance                                                                                       | F <sub>c</sub> =1 MHz (Note 4)                      | 1    | 20                      | pF       |

Notes: 1. The Min value, -0.3, is not 100% tested.

- 2. PEREQ input has an internal pull-down resistor.

- 3. BS16, BUSY, FLT, ERROR, SMI, SMIRDY, and IIBEN inputs each have an internal pull-up resistor.

- 4. Not 100% tested.

- 5. Outputs are CMOS and will pull rail-to-rail if the load is not resistive.

- 6. Von is only valid for SMI when exiting SMM for two CLK2 cycles.

- 7. SMI and IIBEN leakage Low will be ILI when pull-up is inactive and IL when pull-up is active.

- 8. Inputs are at either Vcc or Vss.

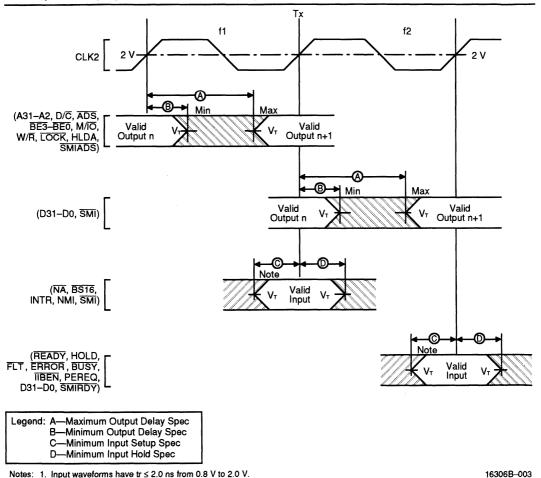

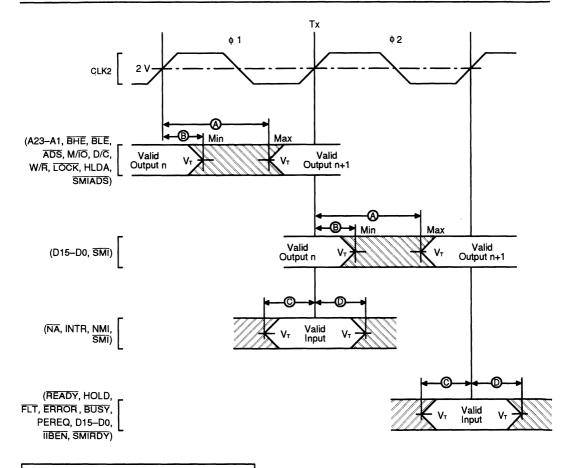

#### **SWITCHING CHARACTERISTICS**

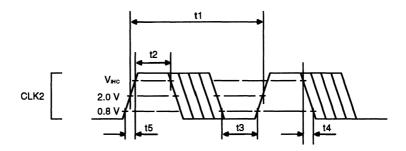

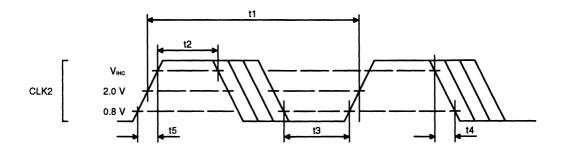

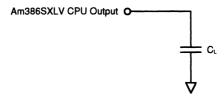

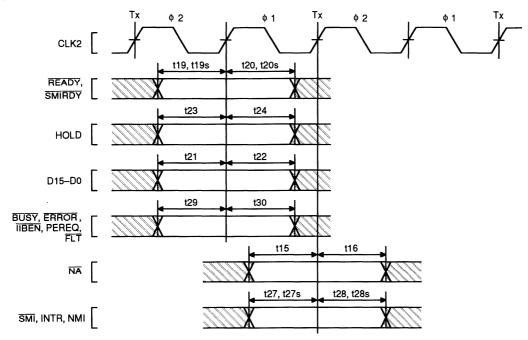

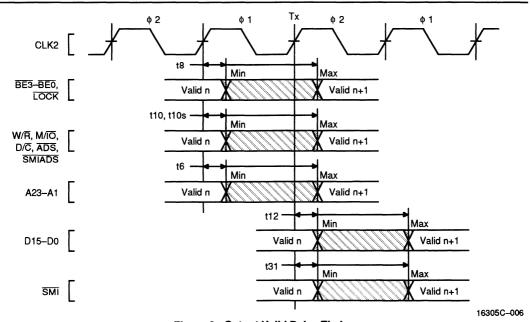

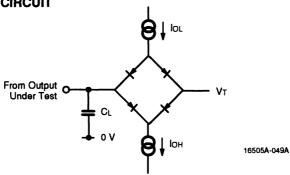

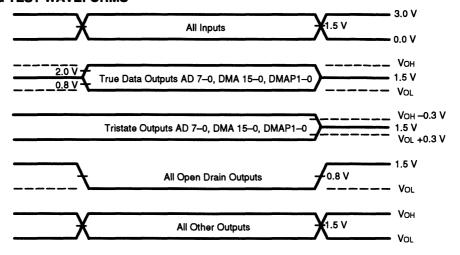

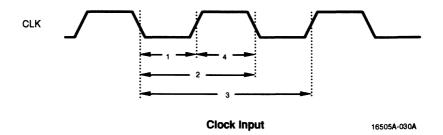

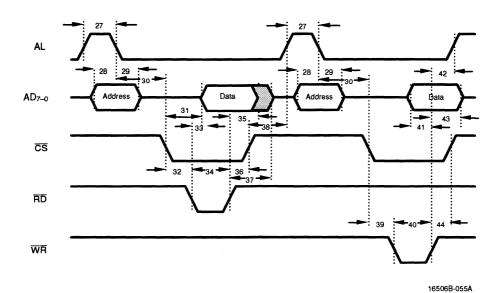

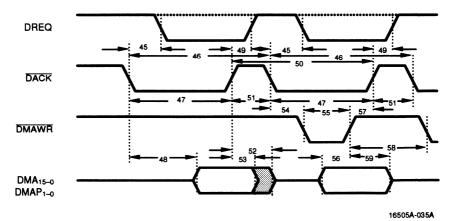

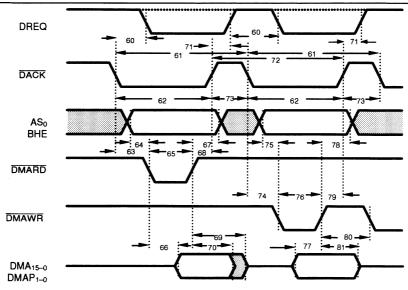

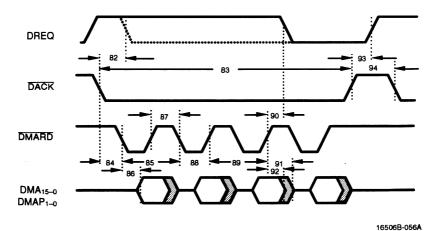

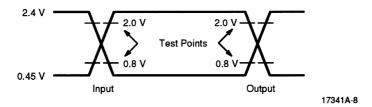

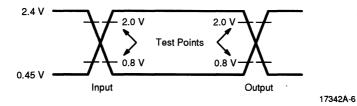

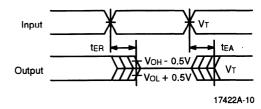

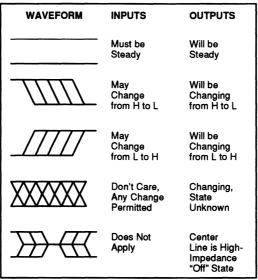

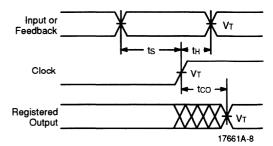

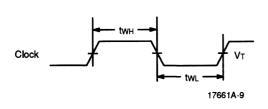

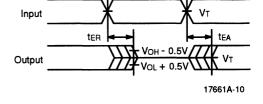

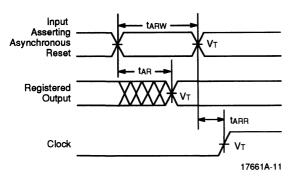

The switching characteristics consist of output delays, input setup requirements, and input hold requirements. All characteristics are relative to the CLK2 rising edge crossing the 2.0-V level.

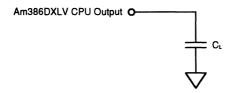

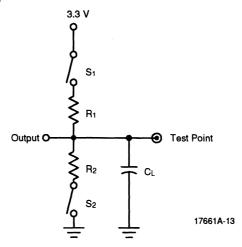

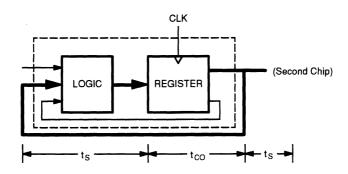

Switching characteristic measurement is defined in Figure 2. Inputs must be driven to the voltage levels indicated by this diagram. Am386DXLV CPU output delays are specified with minimum and maximum limits measured as shown. The minimum Am386DXLV microprocessor delay times are hold times provided to external circuitry. Am386DXLV microprocessor input setup and hold time are specified as minimums, defining the smallest acceptable sampling window. Within the sampling

2.  $V_T = 1.0 \text{ V at } V_{CC} \le 3.6$ ; 1.5 V at  $V_{CC} > 3.6$ .

window, a synchronous input signal must be stable for correct Am386DXLV microprocessor operation.

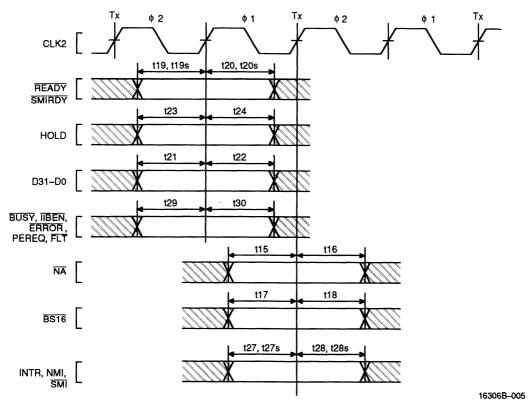

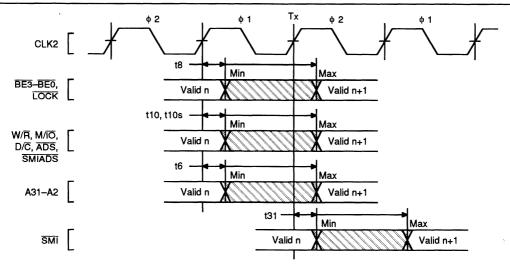

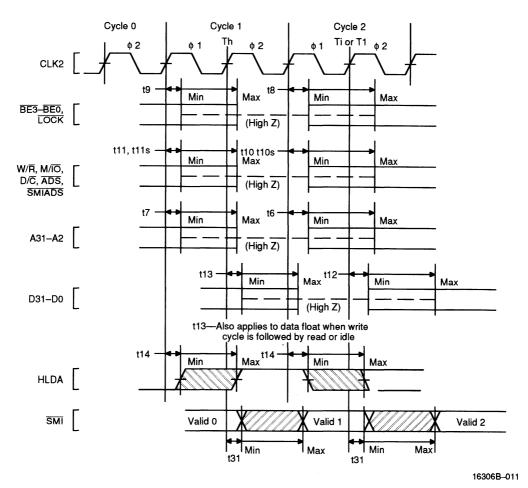

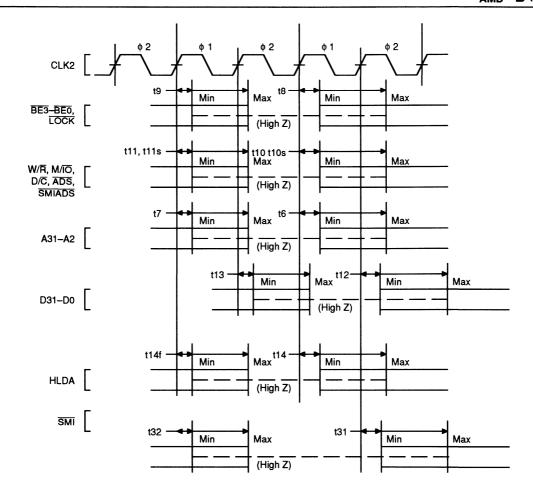

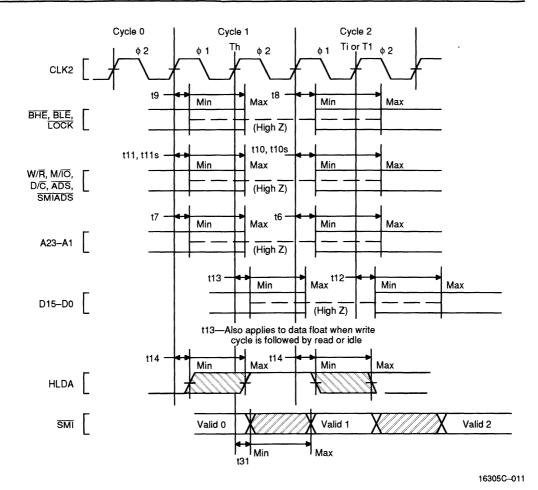

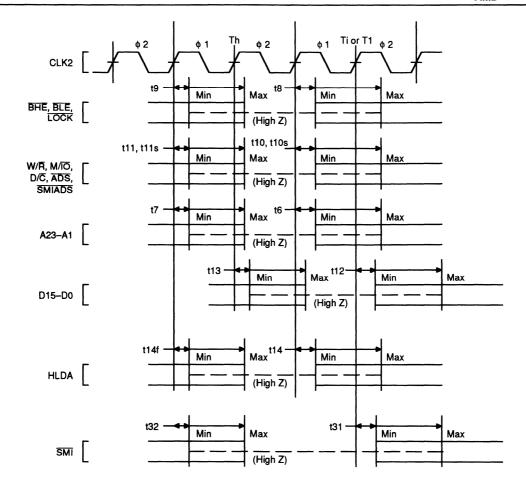

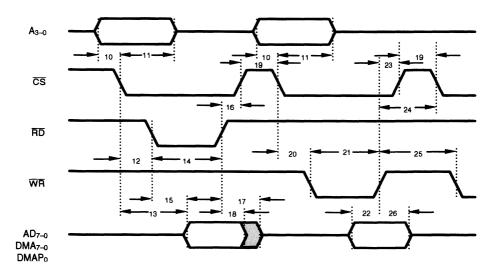

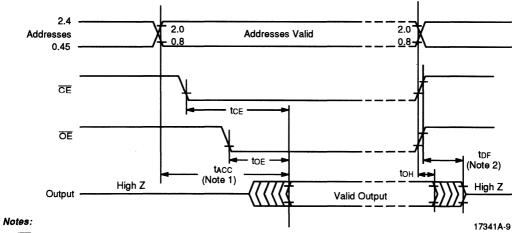

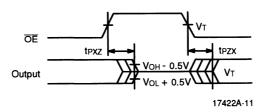

Outputs W/R, D/C, M/IO, LOCK, BE3-BE0, ADS, A31-A2, HLDA, and SMIADS only change at the beginning of phase one. D31-D0 (write cycles) and SMI only change at the beginning of phase two. The READY, HOLD, IIBEN, BUSY, ERROR, PEREQ, FLT, D31-D0, and SMIRDY (read cycles) inputs are sampled at the beginning of phase one. The NA, BS16, INTR, NMI, and SMI inputs are sampled at the beginning of phase two.

Figure 2. Drive Levels and Measurement Points

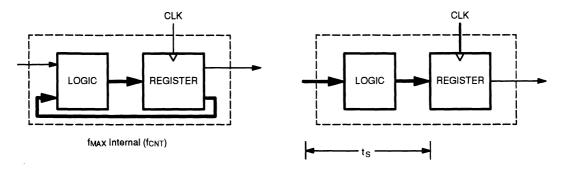

# SWITCHING CHARACTERISTICS over operating range at 25 MHz $V_{\text{CC}}\!=\!3.0$ V to 5.5 V; $T_{\text{CASE}}\!=\!0^{\circ}\text{C}$ to $+100^{\circ}\text{C}$

|     |                                              |                        |             | F   | inal | 7    |

|-----|----------------------------------------------|------------------------|-------------|-----|------|------|

| No. | Parameter Description                        | Notes                  | Ref Figures | Min | Max  | Unit |

|     | Operating Frequency                          | Half of CLK2 Freq      |             | 0   | 25   | MHz  |

| 1   | CLK2 Period                                  |                        | 4           | 20  |      | ns   |

| 2   | CLK2 High Time                               | at V <sub>IHC</sub>    | 4           | 4   |      | ns   |

| 3   | CLK2 Low Time                                | at 0.8 V               | 4           | 5   |      | ns   |

| 4   | CLK2 Fall Time (Note 3)                      | 2.4 V to 0.8 V         | 4           |     | 7    | ns   |

| 5   | CLK2 Rise Time (Note 3)                      | 0.8 V to 2.4 V         | 4           |     | 7    | ns   |

| 6   | A31-A2 Valid Delay                           | C <sub>L</sub> = 50 pF | 3, 6        | 4   | 17   | ns   |

| 7   | A31-A2 Float Delay                           | (Note 1)               | 13          | 4   | 30   | ns   |

| 8   | BE3-BE0, LOCK Valid Delay                    | C <sub>L</sub> = 50 pF | 3, 6        | 4   | 17   | ns   |

| 9   | BE3-BE0, LOCK Float Delay                    | (Note 1)               | 13          | 4   | 30   | ns   |

| 10  | W/R, M/IO, D/C, ADS Valid Delay              | C <sub>L</sub> =50 pF  | 3, 6        | 4   | 17   | ns   |

| 10s | SMIADS Valid Delay                           | C <sub>L</sub> =50pF   | 3, 6        | 4   | 25   | ns   |

| 11_ | W/R, M/IO, D/C, ADS Float Delay              | (Note 1)               | 13          | 4   | 30   | ns   |

| 11s | SMIADS Float Delay                           | (Note 1)               | 13          | 4   | 30   | ns   |

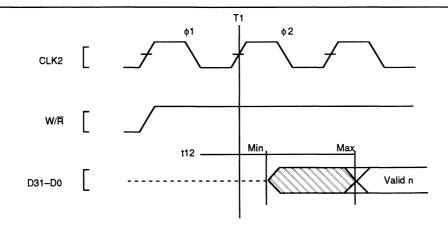

| 12  | D31-D0 Write Data Valid Delay                | C <sub>L</sub> = 50 pF | 6, 7        | 7   | 23   | ns   |

| 12a | D31-D0 Write Data Hold Time                  | C <sub>L</sub> = 50 pF | 3, 8        | 2   |      | ns   |

| 13  | D31-D0 Float Delay                           | (Note 1)               | 13          | 4   | 22   | ns   |

| 14  | HLDA Valid Delay                             | C <sub>L</sub> =50 pF  | 3, 13       | 4   | 22   | ns   |

| 14f | HLDA Float Delay                             | (Note 1)               | 14          | 4   | 30   | ns   |

| 15  | NA Setup Time                                |                        | 5           | 5   |      | ns   |

| 16  | NA Hold Time                                 |                        | 5           | 3   |      | ns   |

| 17  | BS16 Setup Time                              |                        | 5           | 5   |      | ns   |

| 18  | BS16 Hold Time                               |                        | 5           | 3   |      | ns   |

| 19  | READY Setup Time                             |                        | 5           | 9   |      | ns   |

| 19s | SMIRDY Setup Time                            |                        | 5           | 9   |      | ns   |

| 20  | READY Hold Time                              |                        | 5           | 4   | 1    | ns   |

| 20s | SMIRDY Hold Time                             |                        | 5           | 4   |      | ns   |

| 21  | D31-D0 Read Setup Time                       |                        | 5           | 7   |      | ns   |

| 22  | D31-D0 Read Hold Time                        |                        | 5           | 5   |      | ns   |

| 23  | HOLD Setup Time                              |                        | 5           | 9   |      | ns   |

| 24  | HOLD Hold Time                               |                        | 5           | 3   |      | ns   |

| 25  | RESET Setup Time                             |                        | 15          | 8   |      | ns   |

| 26  | RESET Hold Time                              |                        | 15          | 3   |      | ns   |

| 27  | NMI, INTR Setup Time                         | (Note 2)               | 5           | 6   |      | ns   |

| 27s | SMI Setup Time                               |                        | 5           | 6   |      | ns   |

| 28  | NMI, INTR Hold Time                          | (Note 2)               | 5           | _ 6 |      | ns   |

| 28s | SMI Hold Time                                |                        | 5           | 4   |      | ns   |

| 29  | PEREQ, ERROR, BUSY, FLT,<br>IIBEN Setup Time | (Note 2)               | 5           | 6   |      | ns   |

| 30  | PEREQ, ERROR, BUSY, FLT,<br>IIBEN Hold Time  | (Note 2)               | 5           | 5   |      | ns   |

| 31  | SMI Valid Delay                              |                        | 5, 13       | 4   | 22   | ns   |

| 32  | SMI Float Delay                              | (Note 1)               | 14          | 4   | 30   | ns   |

Notes: 1. Float condition occurs when maximum output current becomes less than I<sub>Lo</sub> magnitude. Float delay is not 100% tested.

2. These inputs are allowed to be asynchronous to CLK2. The setup and hold specifications are given for testing purposes, to assure recognition within a specific CLK2 period.

3. Rise and fall times are not tested.

# SWITCHING CHARACTERISTICS over operating range at 33 MHz $V_{\text{CC}}$ = 4.5 V to 5.5 V; $T_{\text{CASE}}$ = 0°C to +100°C

|     |                                              |                        | F           | Final |      |      |

|-----|----------------------------------------------|------------------------|-------------|-------|------|------|

| No. | Parameter Description                        | Notes                  | Ref Figures | Min   | Max  | Unit |

|     | Operating Frequency                          | Half of CLK2 Freq      |             | 0     | 33.3 | MHz  |

| 1   | CLK2 Period                                  |                        | 4           | 15.0  |      | ns   |

| 2   | CLK2 High Time                               | at V <sub>IHC</sub>    | 4           | 4.5   |      | ns   |

| 3   | CLK2 Low Time                                | at 0.8 V               | 4           | 4.5   |      | ns   |

| 4   | CLK2 Fall Time (Note 3)                      | 2.4 V to 0.8 V         | 4           |       | 4    | ns   |

| 5   | CLK2 Rise Time (Note 3)                      | 0.8 V to 2.4 V         | 4           |       | 4    | ns   |

| 6   | A31-A2 Valid Delay                           | C <sub>L</sub> = 50 pF | 3, 6        | 4     | 15   | ns   |

| 7   | A31-A2 Float Delay                           | (Note 1)               | 13          | 4     | 20   | ns   |

| 8   | BE3-BE0, LOCK Valid Delay                    | C <sub>L</sub> = 50 pF | 3, 6        | 4     | 15   | ns   |

| 9   | BE3-BE0, LOCK Float Delay                    | (Note 1)               | 13          | 4     | 20   | ns   |

| 10  | W/R, M/IO, D/C, ADS Valid Delay              | C <sub>L</sub> = 50 pF | 3, 6        | 4     | 15   | ns   |

| 10s | SMIADS Valid Delay                           | C₁=50 pF               | 2, 6        | 4     | 15   | ns   |

| 11  | W/R, M/IO, D/C, ADS Float Delay              | (Note 1)               | 13          | 4     | 20   | ns   |

| 11s | SMIADS Float Delay                           | (Note 1)               | 13          | 4     | 20   | ns   |

| 12  | D31-D0 Write Data Valid Delay                | C <sub>L</sub> = 50 pF | 6, 7        | 7     | 23   | ns   |

| 12a | D31-D0 Write Data Hold Time                  | C <sub>L</sub> = 50 pF | 3, 8        | 2     |      | ns   |

| 13  | D31-D0 Float Delay                           | (Note 1)               | 13          | 4     | 17   | ns   |

| 14  | HLDA Valid Delay                             | C <sub>L</sub> = 50 pF | 3, 13       | 4     | 20   | ns   |

| 14f | HLDA Float Delay                             | (Note 1)               | 14          | 4     | 20   | ns   |

| 15  | NA Setup Time                                |                        | 5           | 5     |      | ns   |

| 16  | NA Hold Time                                 |                        | 5           | 2     |      | ns   |

| 17  | BS16 Setup Time                              |                        | 5           | 5     |      | ns   |

| 18  | BS16 Hold Time                               |                        | 5           | 2     | i i  | ns   |

| 19  | READY Setup Time                             |                        | 5           | 7     |      | ns   |

| 19s | SMIRDY Setup Time                            |                        | 5           | 7     |      | ns   |

| 20  | READY Hold Time                              |                        | 5           | 4     |      | ns   |

| 20s | SMIRDY Hold Time                             |                        | 5           | 4     |      | ns   |

| 21  | D31-D0 Read Setup Time                       |                        | 5           | 5     |      | ns   |

| 22  | D31-D0 Read Hold Time                        |                        | 5           | 3     |      | ns   |

| 23  | HOLD Setup Time                              |                        | 5           | 9     |      | ns   |

| 24  | HOLD Hold Time                               |                        | 5           | 2     |      | ns   |

| 25  | RESET Setup Time                             |                        | 15          | 5     |      | ns   |

| 26  | RESET Hold Time                              |                        | 15          | 2     |      | ns   |

| 27  | NMI, INTR Setup Time                         | (Note 2)               | 5           | 5     |      | ns   |

| 27s | SMI Setup Time                               | 1                      | 5           | 5     |      | ns   |

| 28  | NMI, INTR Hold Time                          | (Note 2)               | 5           | 5     |      | ns   |

| 28s | SMI Hold Time                                |                        | 5           | 4     |      | ns   |

| 29  | PEREQ, ERROR, BUSY, FLT,<br>IIBEN Setup Time | (Note 2)               | 5           | 5     |      | ns   |

| 30  | PEREQ, ERROR, BUSY, FLT, IIBEN Hold Time     | (Note 2)               | 5           | 4     |      | ns   |

| 31  | SMI Valid Delay                              | 1,                     | 5, 13       | 4     | 17   | ns   |

| 32  | SMI Float Delay                              | (Note 1)               | 14          | 4     | 20   | ns   |

Notes: 1. Float condition occurs when maximum output current becomes less than I<sub>LO</sub> in magnitude. Float delay is not 100% tested.

2. These inputs are allowed to be asynchronous to CLK2. The setup and hold specifications are given for testing purposes, to assure recognition within a specific CLK2 period.

3. Rise and fall times are not tested.

#### **SWITCHING CHARACTERISTICS (continued)**

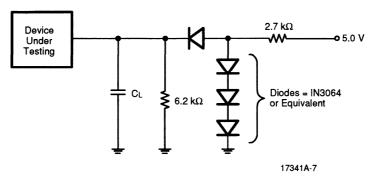

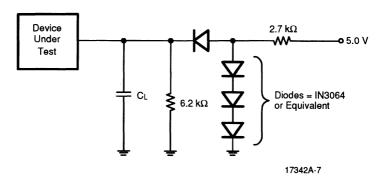

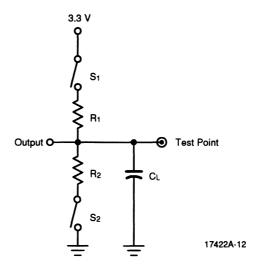

C<sub>L</sub> includes all parasitic capacitances.

15021B-072

Figure 3. AC Test Load

Figure 4. CLK2 Timing

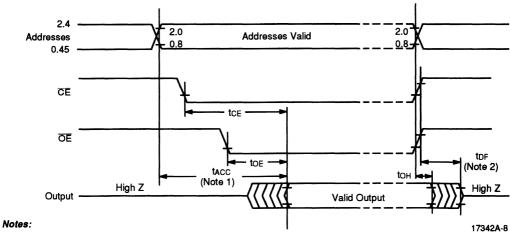

#### **SWITCHING WAVEFORMS**

Figure 5. Input Setup and Hold Timing

Figure 6. Output Valid Delay Timing

15021B-076

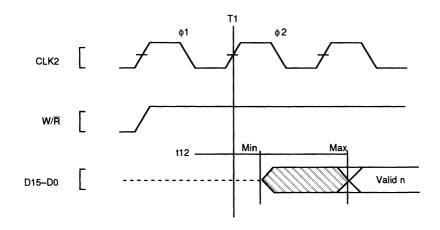

Figure 7. Write Data Valid Delay Timing

Figure 8. Write Data Hold Timing

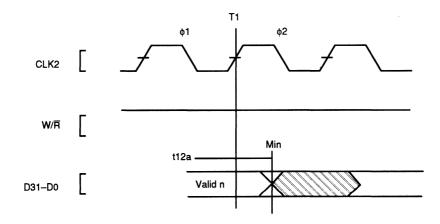

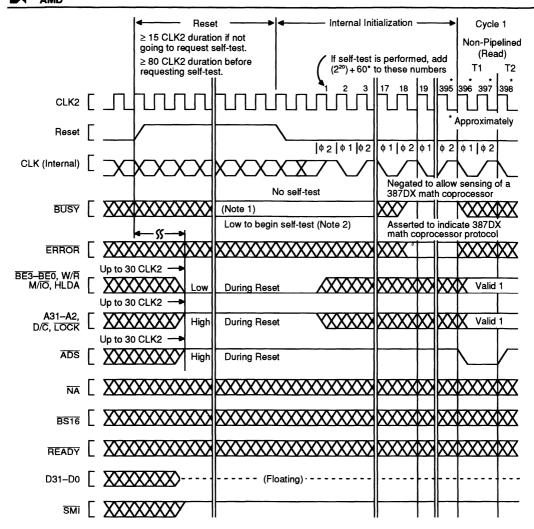

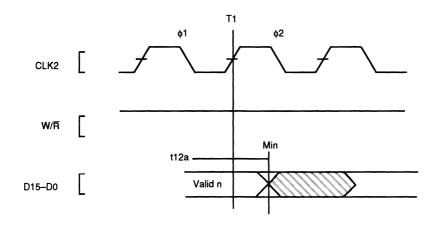

Notes: 1. BUSY should be held stable for eight CLK2 periods before and after the CLK2 period in which RESET falling edge occurs.

2. If self-test is requested, the Am386DXLV microprocessor outputs remain in their reset state as shown here.

sted, the Am386DXLV microprocessor outputs remain in their reset state as shown here.

16306B-007

\*Once initiated, the system must hold \$\overline{SMI}\$ Low until the first \$\overline{SMIADS}\$. At this time, the system releases control of \$\overline{SMI}\$ and can not drive \$\overline{SMI}\$ until three CLK2 cycles after the CPU drives \$\overline{SMI}\$ High. CPU will drive \$\overline{SMI}\$ High for two CLK2 cycles. The additional clock allows the CPU to completely release \$\overline{SMI}\$ and prevents any driver overlap.

16306B-009

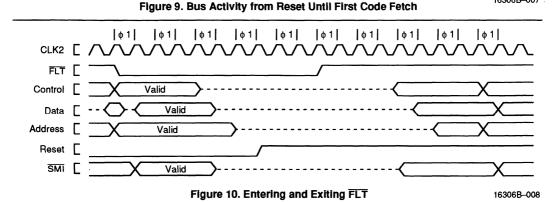

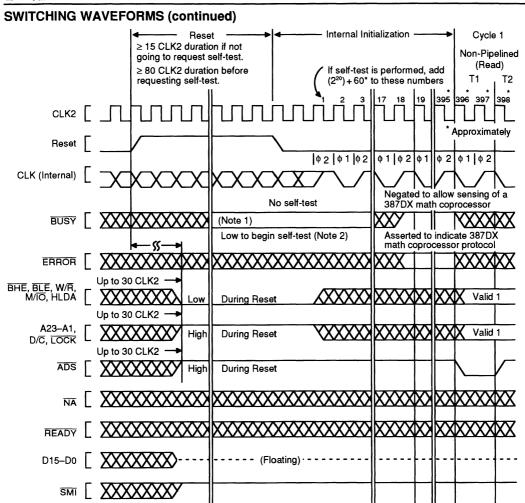

Figure 11. Initiating and Exiting SMM

Figure 12. RESET and SMI

Figure 13. Output Float Delay and HLDA and SMI Valid Delay Timing

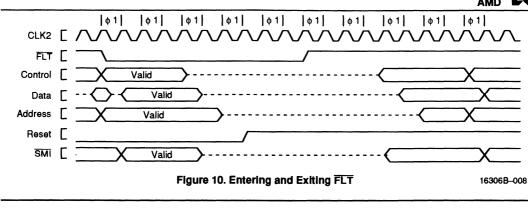

Figure 14. Output Float Delay Entering and Exiting FLT

16306B-012

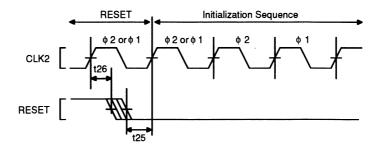

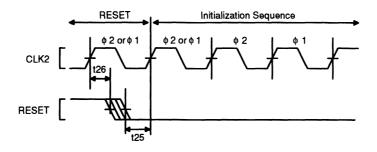

The second internal processor phase following RESET High-to-Low transition (provided t25 and t26 are met) is  $\phi 2$ .

Figure 15. RESET Setup and Hold Timing and Internal Phase

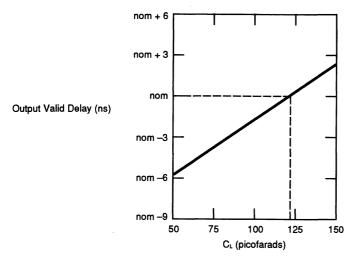

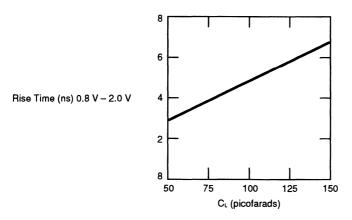

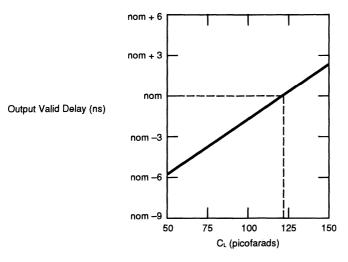

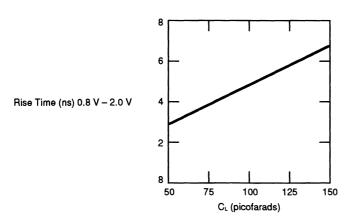

Note: This graph will not be linear outside the C<sub>L</sub> range shown.

15021B-079

Figure 16. Typical Output Valid Delay Versus Load Capacitance at Maximum Operating Temperature (C<sub>L</sub>=120 pF)

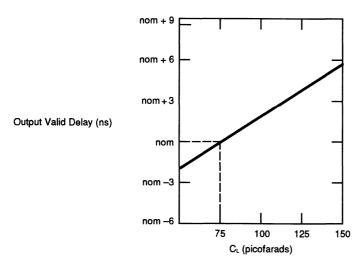

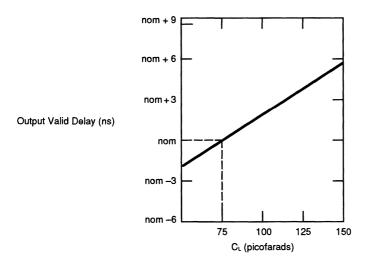

Note: This graph will not be linear outside the C<sub>L</sub> range shown.

Figure 17. Typical Output Valid Delay Versus Load Capacitance at Maximum Operating Temperature ( $C_L = 75 \text{ pF}$ )

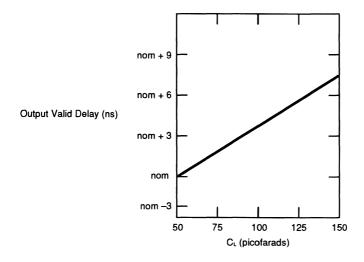

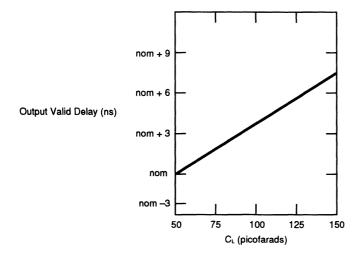

Note: This graph will not be linear outside the C<sub>L</sub> range shown.

Figure 18. Typical Output Valid Delay Versus Load Capacitance at Maximum Operating Temperature (C<sub>L</sub> = 50 pF)

15021B-081

Note: This graph will not be linear outside the CL range shown.

Figure 19. Typical Output Rise Time Versus Load Capacitance at Maximum Operating Temperature

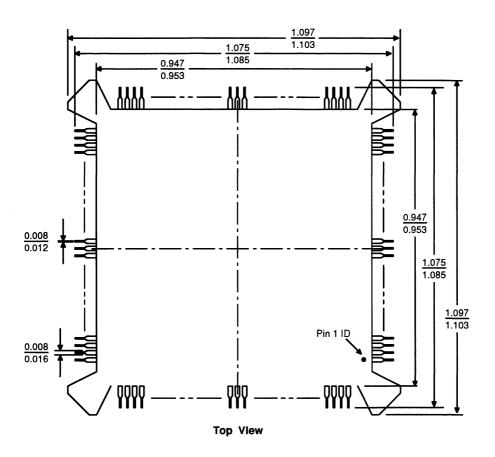

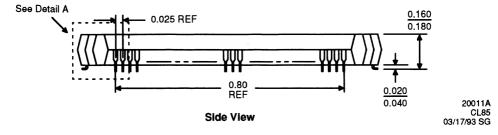

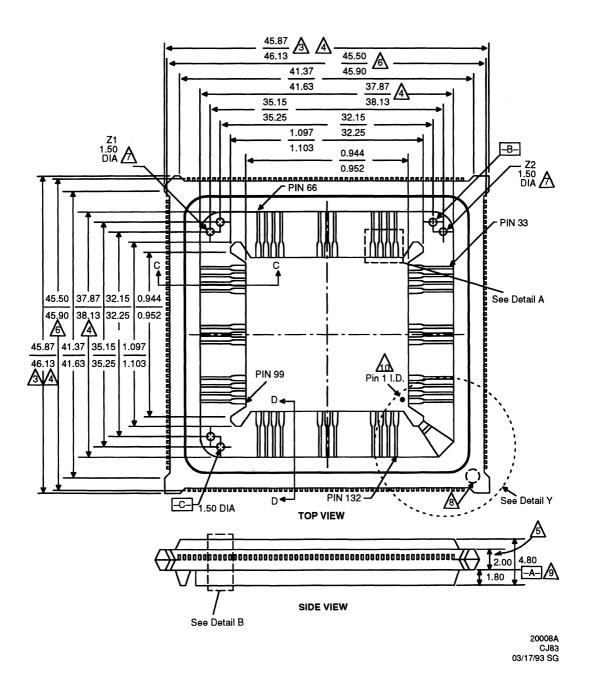

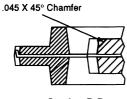

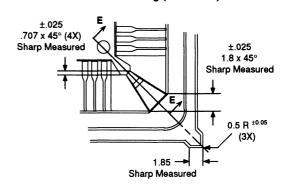

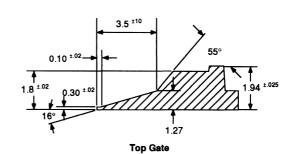

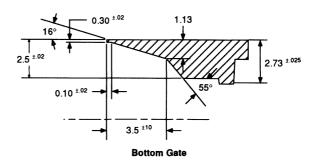

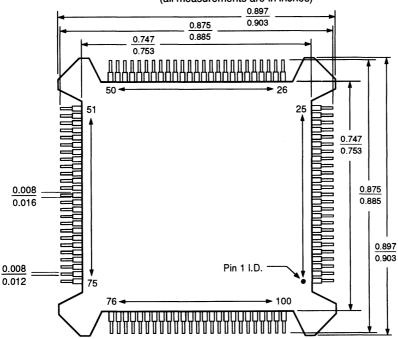

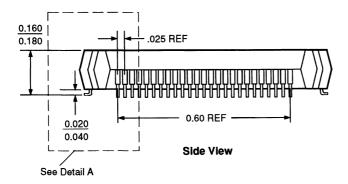

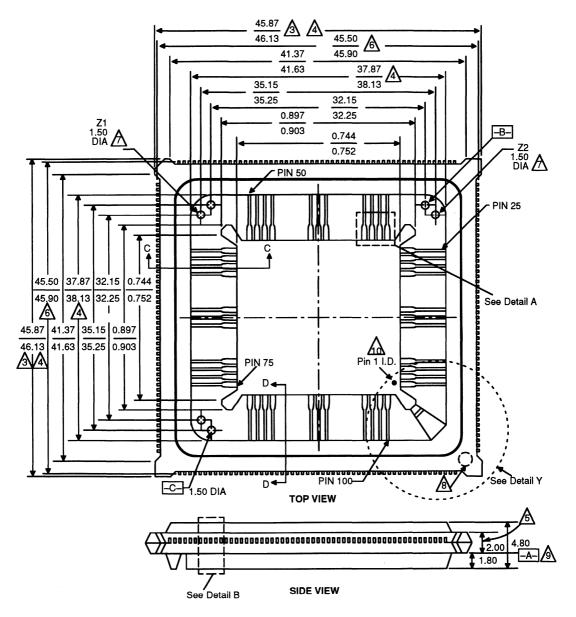

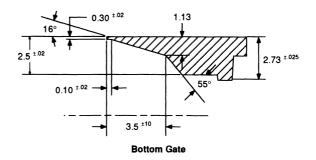

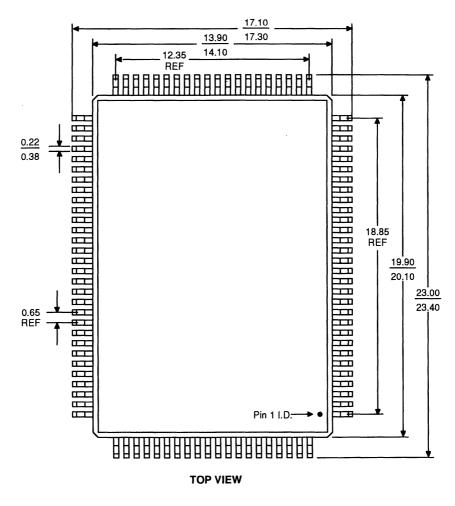

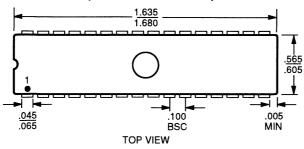

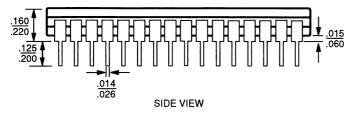

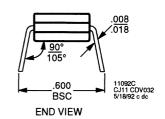

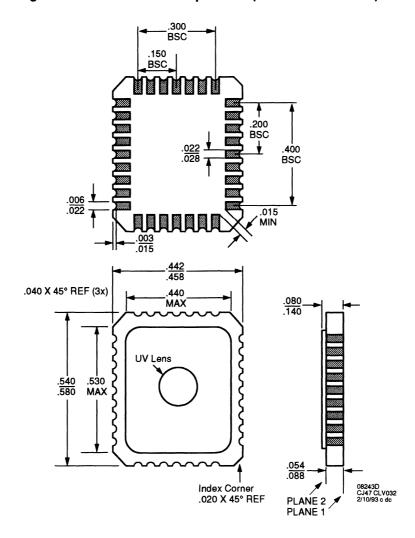

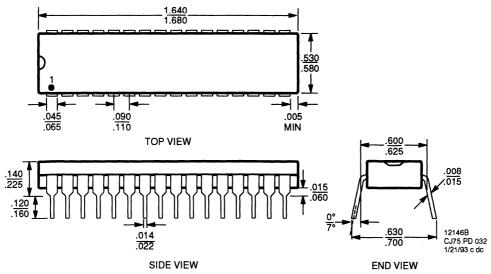

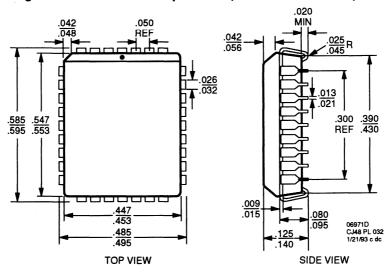

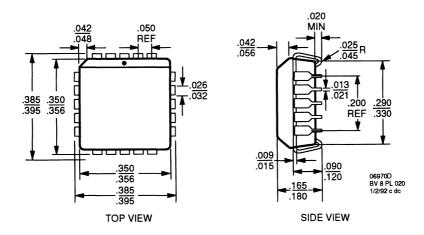

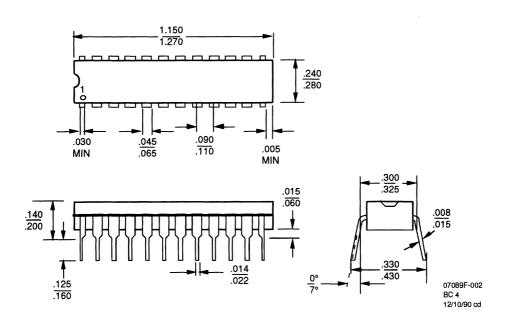

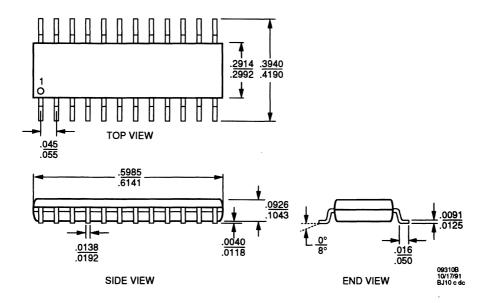

#### **PHYSICAL DIMENSIONS**

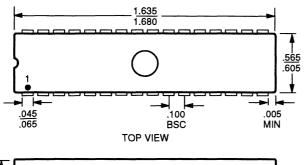

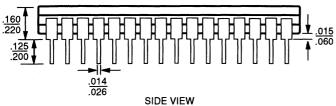

For reference only. All dimensions are in inches, except for the outer ring on PQB 132 which is in millimeters. BSC is an ANSI standard for Basic Space Centering.

PQB 132—Plastic Quad Flat Pack; Trimmed and Formed (all measurements in inches)

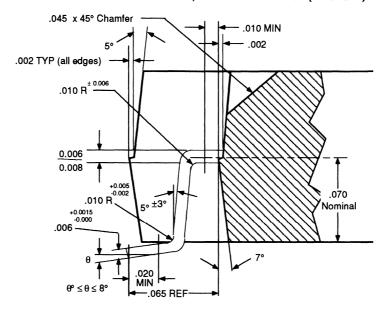

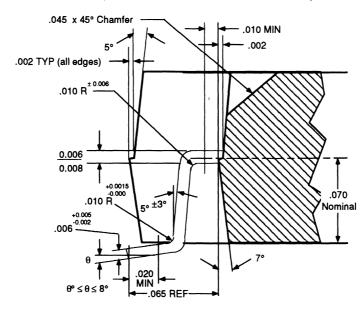

#### **PHYSICAL DIMENSIONS (continued)**

#### PQB 132—Plastic Quad Flat Pack; Trimmed and Formed (continued)

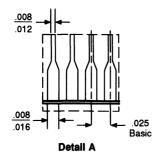

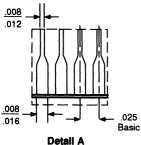

#### **Detail A**

#### Notes:

- 1. All dimensions are in inches unless otherwise specified.

- 2. Dimensions do not include mold protrusion.

- Coplanarity of all leads will be within 0.004 inches measured from the seating plan. Coplanarity is measured per specification 06–500.

- 4. Deviation from Lead-tip true position shall be within  $\pm 0.003$  inches.

- 5. Half span (center of package to lead-tip) shall be within  $\pm 0.0085$  inches.

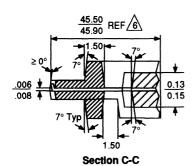

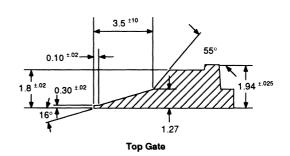

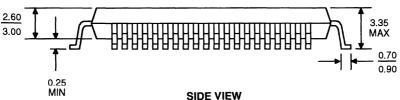

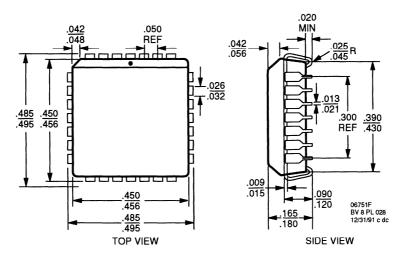

#### **PHYSICAL DIMENSIONS (continued)**

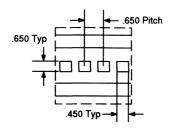

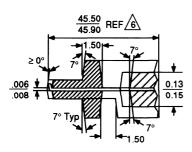

PQB 132—Plastic Quad Flat Pack with Molded Carrier Ring (Inner device measured in inches; outer ring measured in millimeters)

# PQB 132—Plastic Quad Flat Pack with Molded Carrier Ring (continued)

Detail B

**Section C-C**

Section D-D

Detail Y

Section E-E

#### PQB 132 — Plastic Quad Flat Pack with Molded Carrier Ring

#### Notes:

- 1. All dimensions and tolerances conform to ANSI Y14.5M-1982.

- 2. Controlling dimensions: package is measured in inches and ring is measured in millimeters.

- 3. These dimensions do not include mold protrusion. Allowable mold protrusion is 0.2 mm per side.

- 4. These dimensions include mold mismatch and are measured at the parting line.

- 5. Dimensions are centered about centerline of lead material.

- 6. These dimensions are from the outside edge to the outside edge of the test points.

- 7. There are six locating holes in the ring. –B– and –C– datum holes are used for trim form and excise of the molded package only. Holes Z1 and Z2 are used for electrical testing only.

- 8. This area is reserved for vacuum pickup on each of the four corners of the ring and must be flat within 0.025 mm. No ejector pins in this area.

- 9. Datum -A- surface for seating in socket applications.

- 10. Pin one orientation with respect to carrier ring as indicated.

# Am386SXLV

High-Performance, Low-Voltage, 32-Bit Microprocessor with 16-Bit Data Bus

#### **DISTINCTIVE CHARACTERISTICS**

- Operating range 3.0 V to 5.5 V—Ideal for notebook PC designs

- -25-MHz operating frequency for 3.0 V-5.5 V

- -33-MHz operating frequency for 4.5 V-5.5 V

- Twice the battery life of existing 5-V designs

- Wide range of chipsets and other logic available for 3-V systems with support for Standby Mode operation

- -True static design for long battery life

- Power consumption 75% lower than Intel i386SX, 65% lower than Am386SXL microprocessor

- -Performance on demand (0 to 25 MHz)

- System Management Mode (SMM) for system and power management

- System Management Interrupt (SMI) for power management independent of processor operating mode and operating system

- —SMI coupled with I/O instruction break feature provides transparent power off and auto resume of peripherals which may not be "power aware"

- —SMI is non-maskable and has higher priority than Non-Maskable Interrupt (NMI)

- Automatic save and restore of the microprocessor state

- Wide range of chipsets supporting SMM available to allow product differentiation

- Lower heat dissipation for fanless systems

- "Float" input to facilitate system debug and test

- Compatible with 386SX systems and software

- Supports 387SX-compatible math coprocessors

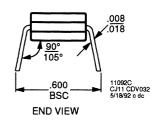

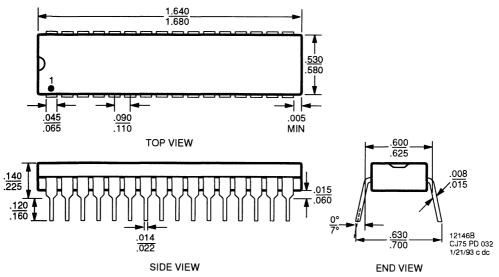

- 100-pin PQFP package with optional protective ring for better lead coplanarity

- AMD advanced 0.8 micron CMOS technology

O Intel i386SX @ 5.0 V

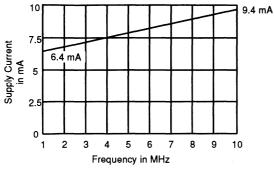

▲ Am386SXL CPU @ 5.0 V

Am386SXLV CPU @ 3.3 V

Note: Inputs at Vcc or Vss.

**Typical Power Consumption**

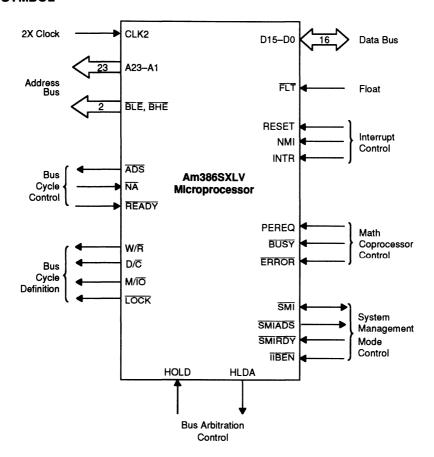

# **BLOCK DIAGRAM**

#### **GENERAL DESCRIPTION**

The Am386SXLV microprocessor is a low-voltage, true static implementation of the Intel i386SX microprocessor. With the operating range of 3.0 V to 5.5 V, the Am386SXLV CPU is ideal for both desktop and battery-powered notebook personal computers. For desktop PCs, this device offers lower heat dissipation, allowing system designers to remove or reduce the size and cost of the cooling fan. The Am386SXLV microprocessor operates at a maximum speed of 25 MHz from 3.0 V–5.5 V and at maximum speed of 33 MHz from 4.5 V–5.5 V.

The Am386SXLV microprocessor's lower operating voltage and true static design enables longer battery life

and/or lower weight for notebook applications. At 20 MHz, this device has 60% lower operating lcc than the Intel i386SX. Lowering typical operating voltage from 5.0 V to 3.3 V doubles the battery life. Standby Mode allows the Am386SXLV microprocessor to be clocked down to 0 MHz (DC) and retain full register contents. In Standby Mode, typical current draw is less than 0.01 mA, a greater than 1000X reduction in power consumption versus the Intel i386SX.

The Am386SXLV microprocessor is available in a small footprint 100-pin Plastic Quad Flat Pack (PQFP) package. This package may be shipped in an optional protective ring for better lead protection during shipping.

Additionally, the Am386SXLV microprocessor comes with System Management Mode (SMM) for system and power management. SMI (System Management Interrupt) is a non-maskable, higher priority interrupt than NMI and has its own code space (1 Mb in Real Mode and 16 Mb in Protected Mode). SMI can be coupled with the I/O instruction break feature to implement transparent power management of peripherals. SMM can be used by system designers to implement system and power management code independent of the operating system or the processor mode.

The Am386SXLV microprocessor incorporates a float pin that places all outputs in a three-state mode to facilitate board test and debug.

#### **FUNCTIONAL DESCRIPTION**

#### **Benefits of Lower Operating Voltage**

The Am386SXLV microprocessor has an operating voltage range of 3.0 V to 5.5 V. Low voltage allows for lower operating power consumption, longer battery life, and/or smaller batteries for notebook applications.

Because power is proportional to the square of the voltage, reduction of the supply voltage from 5.0 V to 3.3 V reduces power consumption by 56%. This directly translates to a doubling of battery life for portable applications. Lower power consumption can also be used to reduce the size and weight of the battery. Thus, 3.3-V designs facilitate a reduction in the form factor.

A lower operating voltage results in a reduction of I/O voltage swings. This reduces noise generation and provide a less hostile environment for board design. Lower Operating Voltage also reduces electromagnetic radiation noise and makes to obtain FCC approval easier to obtain.

#### SMM—System Management Mode

The Am386SXLV microprocessor has a new System Management Mode (SMM) for system and power management. This mode consists of two features: System Management Interrupt (SMI) and I/O instruction break.

#### SMI—System Management Interrupt

SMI is implemented by using special bus interface pins. This interrupt method can be used to perform system management functions such as power management independent of processor operating mode (Real, Protected, or Virtual 8086 Modes).

SMI can also be invoked in software. This allows system software to communicate with SMI power management code. In addition, the UMOV instruction allows data transfers between SMI and normal system memory spaces.

Activating the SMI pin invokes a sequence that saves the operating state of the processor into a separate SMM memory space, independent of the main system memory. After the state is saved, the processor is forced into Real Mode and begins execution at address

FFFF0h in the SMM memory space where a far jump to the SMM code is executed. This Real Mode code can perform its system management function and then resume execution of the normal system software by executing an RES3 instruction which will reload the saved processor state and continue execution in the main system memory space. See Figure 1 for a general flow-chart of an SMM operation.

Figure 1. Sivily Flo

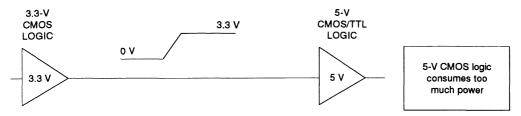

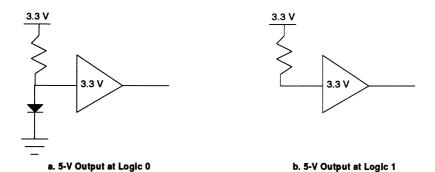

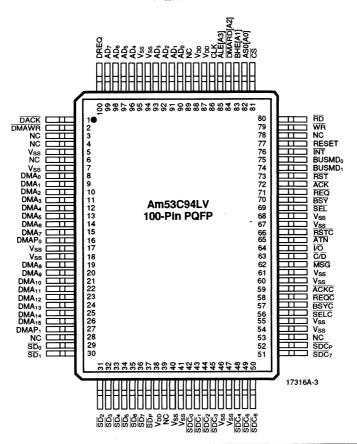

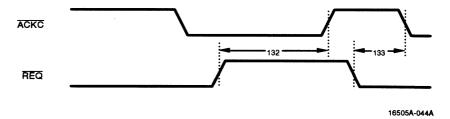

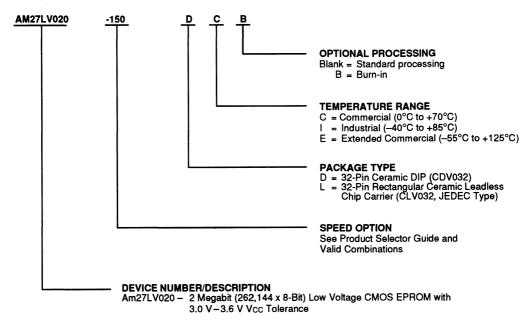

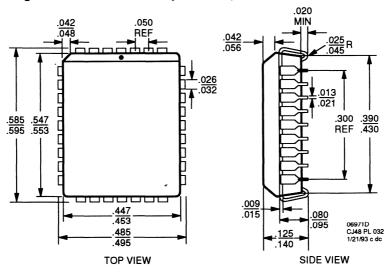

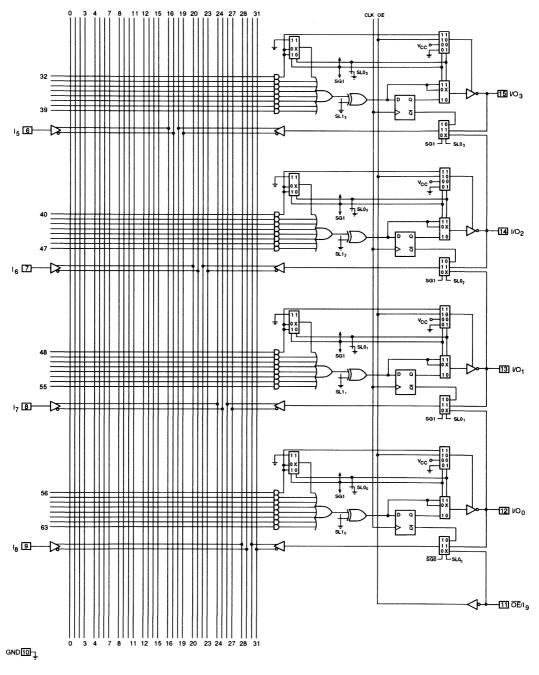

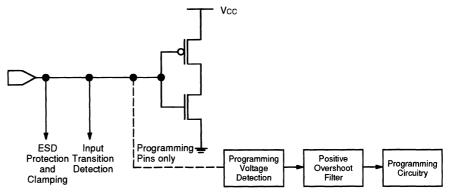

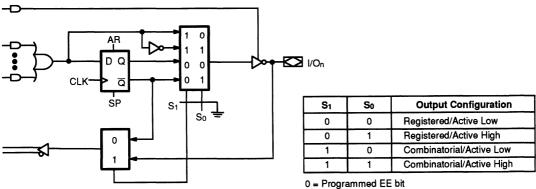

#### **CPU Interface—Pin Functions**